**Design Engineer's Reference Series**

# microNOVA<sup>®</sup>INTEGRATED CIRCUITS DATA MANUAL

## Notice

Data General Corporation (DGC) has prepared this document for use by DGC personnel, customers, and prospective customers. The information contained herein shall not be reproduced in whole or in part without DGC's prior written approval.

DGC reserves the right to make changes in specifications and other information contained in this document without prior notice, and the reader should in all cases consult DGC to determine whether any such changes have been made.

THE TERMS AND CONDITIONS GOVERNING THE SALE OF DGC HARDWARE PRODUCTS AND THE LICENSING OF DGC SOFTWARE CONSIST SOLELY OF THOSE SET FORTH IN THE WRITTEN CONTRACTS BETWEEN DGC AND ITS CUSTOMERS. NO REPRESENTATION OR OTHER AFFIRMATION OF FACT CONTAINED IN THIS DOCUMENT INCLUDING BUT NOT LIMITED TO STATEMENTS REGARDING CAPACITY, RESPONSE-TIME PERFORMANCE, SUITABILITY FOR USE OR PERFORMANCE OF PRODUCTS DESCRIBED HEREIN SHALL BE DEEMED TO BE A WARRANTY BY DGC FOR ANY PURPOSE, OR GIVE RISE TO ANY LIABILITY OF DGC WHATSOEVER.

IN NO EVENT SHALL DGC BE LIABLE FOR ANY INCIDENTAL, INDIRECT, SPECIAL OR CONSEQUENTIAL DAMAGES WHATSOEVER (INCLUDING BUT NOT LIMITED TO LOST PROFITS) ARISING OUT OF OR RELATED TO THIS DOCUMENT OR THE INFORMATION CONTAINED IN IT, EVEN IF DGC HAS BEEN ADVISED, KNEW OR SHOULD HAVE KNOWN OF THE POSSIBILITY OF SUCH DAMAGES.

NOVA, INFOS, ECLIPSE, DASHER and microNOVA are registered trademarks of Data General Corporation, and AZ-TEXT, DG/L, ECLIPSE MV/8000, ENTERPRISE, METEOR, PROXI, REV-UP, SWAT, XODIAC, GENAP, and TRENDVIEW are trademarks of Data General Corporation.

> Ordering No. 014-000074 <sup>©</sup> Data General Corporation, 1976, 1977, 1981 All Rights Reserved Printed in the United States of America Rev. 04, September 1981

# CONTENTS

**Un Data General** Data General Corporation, Westboro, Massachusetts 01581

# OVERVIEW OF microNOVA LINE INTEGRATED CIRCUITS

# OVERVIEW

1

## INTRODUCTION

is data manual describes Data General's full microcomputer chip set. The microcomputer consists of three principal tegrated circuits: a 16-bit microprocessor, an I/O controller, and a 4Kx1 dynamic RAM. As part of the set, each integrated rouit is supported by the necessary system buffer elements. The principal chips are fabricated with N-channel, silicon gate, etal oxide semiconductor (NMOS) technology. The system buffer chips are small and medium scale integration, bi-polar rouits.

te chip set is designed to implement high-performance microcomputer or controller systems. It incorporates Data General's overful NOVA line minicomputer instruction set and 16-bit central processing unit (CPU) architecture.

icroNOVA line integrated circuits are available on an individual basis as well as in full microcomputer chip sets. In addition, the icroNOVA family includes the following supporting hardware.

- CPU boards

- RAM memory boards

- programmable read-only memory boards

- asynchronous interface boards

- general purpose I/O boards

- power supply

- hand-heid console

- card cages

- a variety of peripheral devices; such as:

- video displays

- hard copy data terminals

- single and dual diskette sub-systems

- line printers

- paper tape reader

he microNOVA family comes with proven Data General development and runtime software that includes three operating ystems, the diskette-based Disc Operating System (DOS), the Real-Time Operating System (RTOS), and the icroproducts Operating System (MP/OS). Software developed for Data General's NOVA line minicomputers can be asily reassembled for use with microNOVA systems. The operating systems support two high level language compilers, ORTRAN IV and extended BASIC, as well as various utilities, including: a Command Line Interpreter, text editor, macro ssembler, relocatable loader, a library file editor, and a symbolic debugger.

icroNOVA development software is based on the Disc Operating System. The diskette-based DOS provides a smooth flow rough varying development phases to completed production software. OEMs who need a larger development system can utilize e NOVA 3 line of minicomputers. NOVA 3 is software-compatible with microNOVA and supports up to 128K words of memory, a II peripheral range, and the Real-time Disc Operating System (RDOS).

ata General's Real-Time Operating System is a DOS-compatible runtime executive. It is compact and memory-resident, and as a real-time multitask capability for controlling real-time applications. RTOS provides standard interrupt servicing, device andling and execution scheduling functions.

II of these features make the microNOVA family ideal for applications like complex instrumentation, industrial automation, ommunications, and data acquisition, where 16-bit NOVA power and precision are required.

## microNOVA FUNCTIONAL BLOCK DIAGRAM

1

Data General Corporation, Westboro, Massachusetts 01581

# **OVERVIEW**

## THE CHIP SET

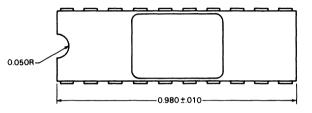

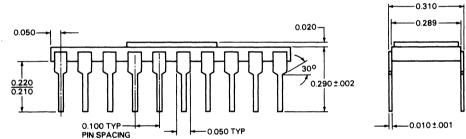

Data General's microcomputer chip set consists of the following dual-in-line packaged (DIP), integrated circuits:

| Integrated Circuit                     | Packaging      |

|----------------------------------------|----------------|

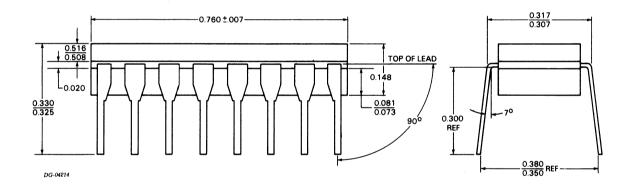

| mN601 16-bit microprocessor            | 40-pin ceramic |

| mN602 16-bit microprocessor            | 40-pin ceramic |

| mN603/613/615 I/O controller (IOC)     | 40-pin ceramic |

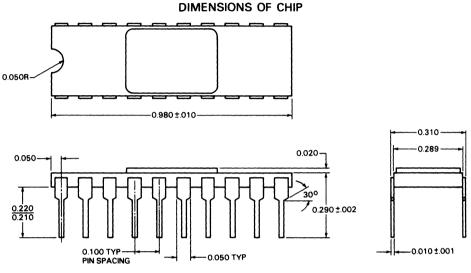

| mN606 4Kx1 dynamic RAM                 | 20-pin plastic |

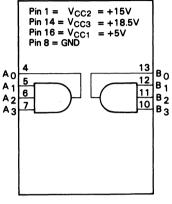

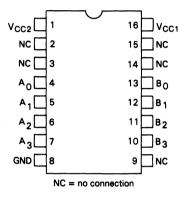

| mN640 CPU and I/O clock driver         | 16-pin cerdip  |

| mN638 memory clock driver              | 16-pin cerdip  |

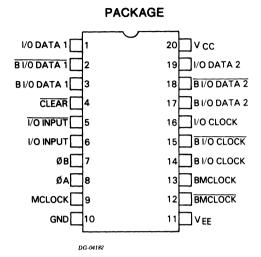

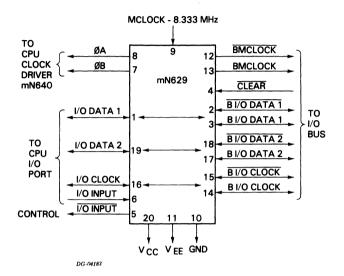

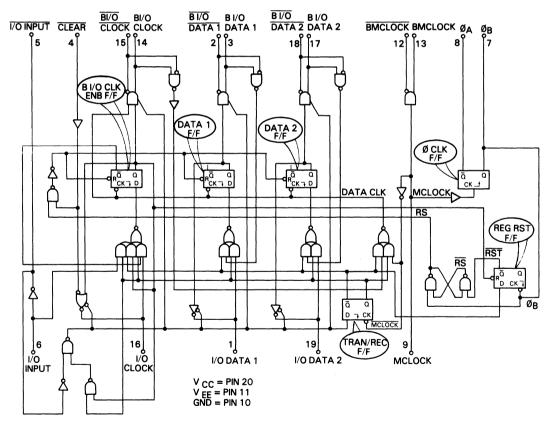

| mN629 CPU I/O transceiver              | 20-pin ceramic |

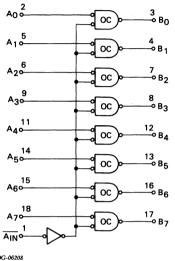

| mN633 octal driver                     | 20-pin ceramic |

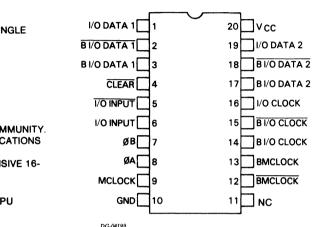

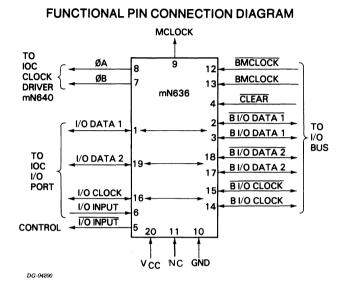

| mN636 IOC I/O transceiver              | 20-pin ceramic |

| mN634 octal memory transceiver         | 20-pin ceramic |

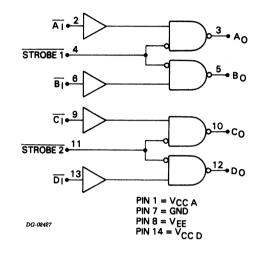

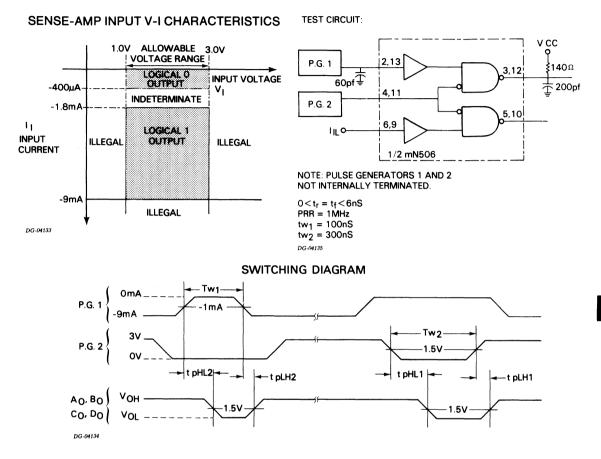

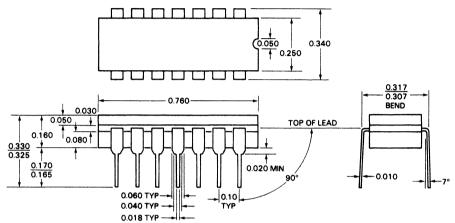

| mN506 quad sense amp/memory bus driver | 14-pin cerdip  |

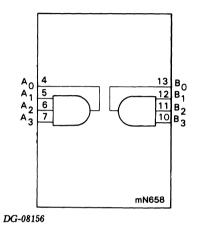

| mN658 I/O clock driver                 | 16 pin cerdip  |

### THE MICROCOMPUTER

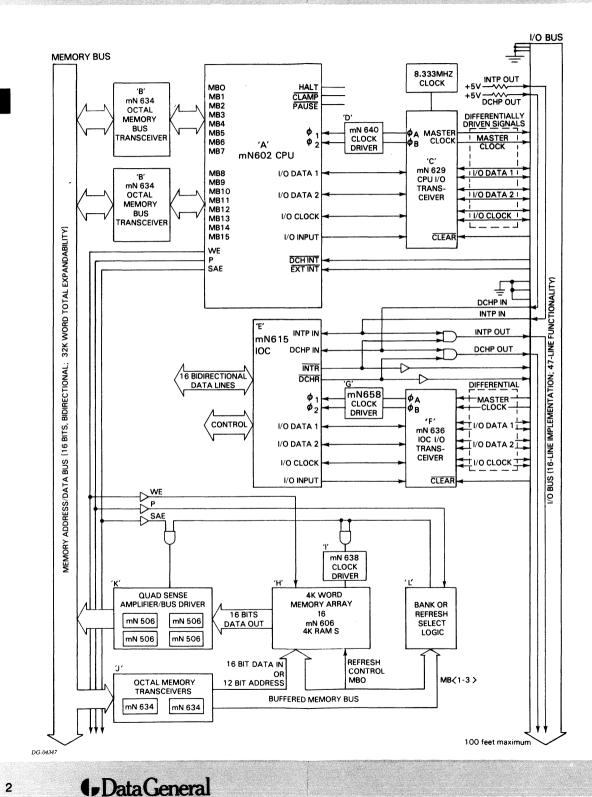

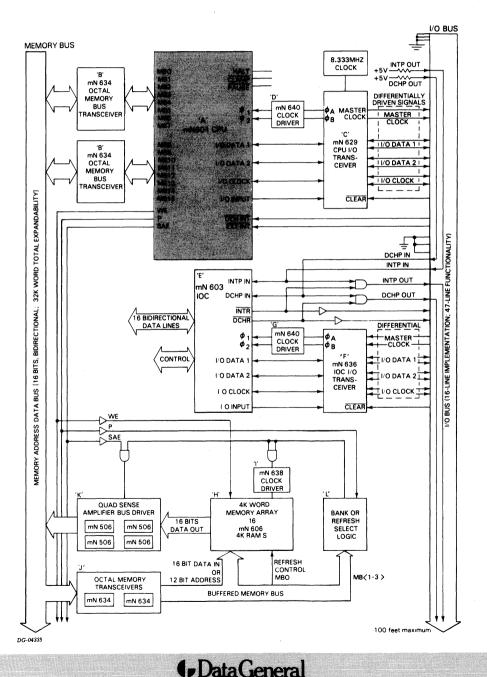

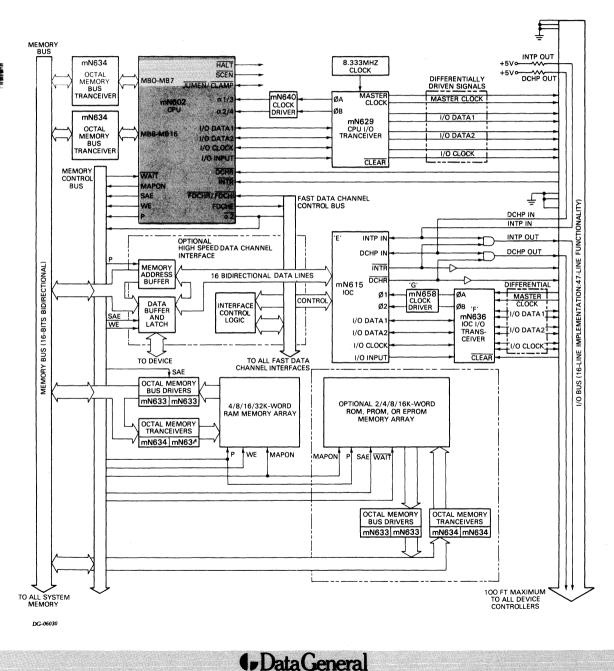

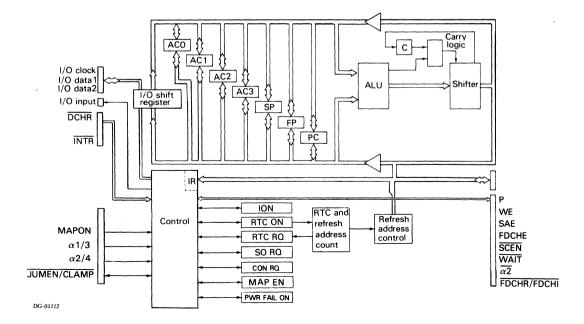

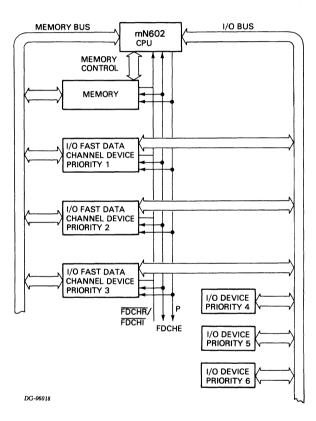

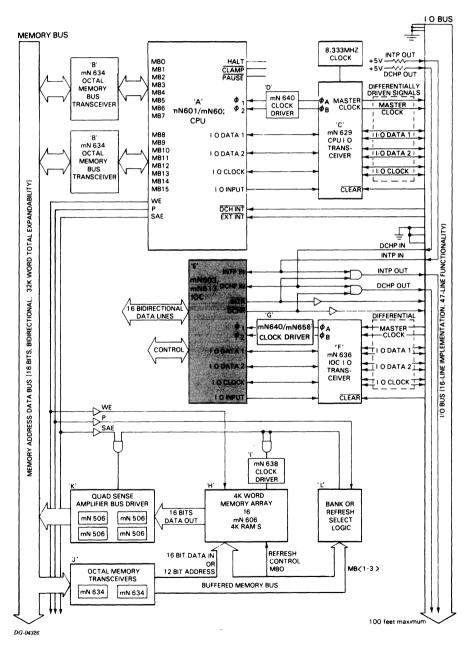

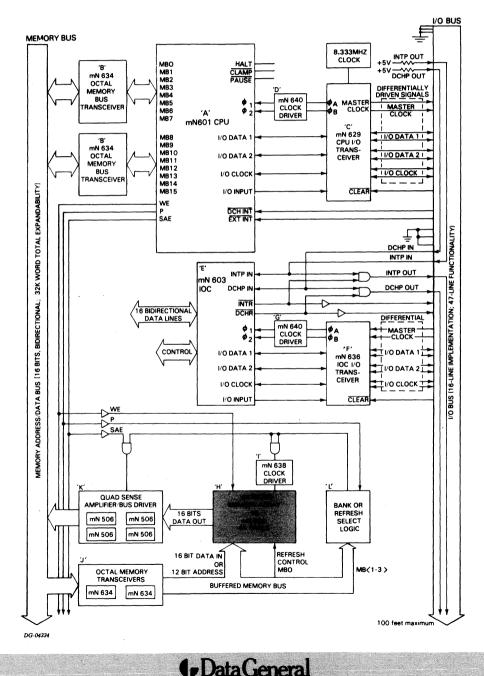

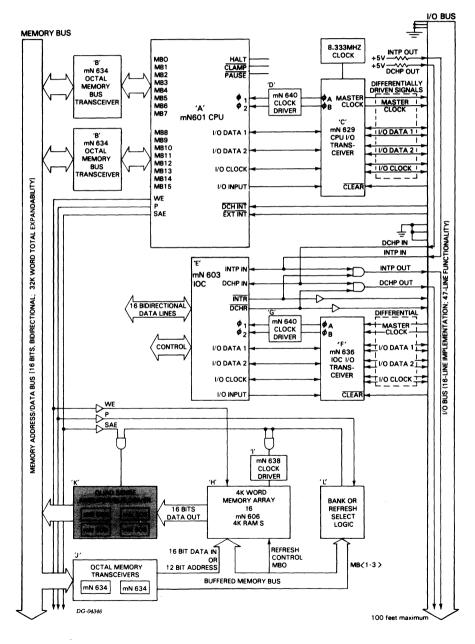

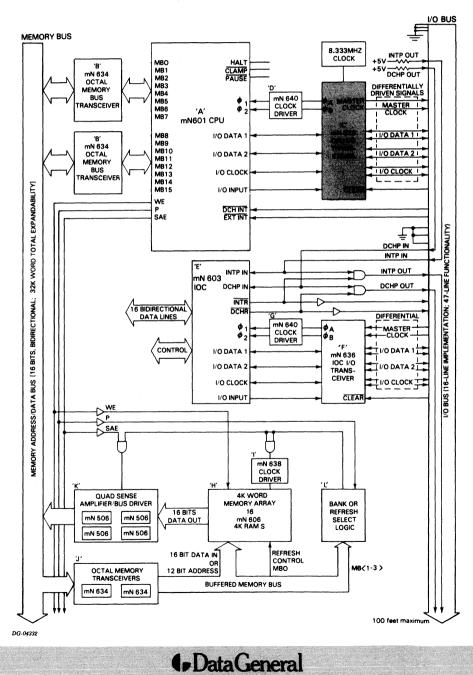

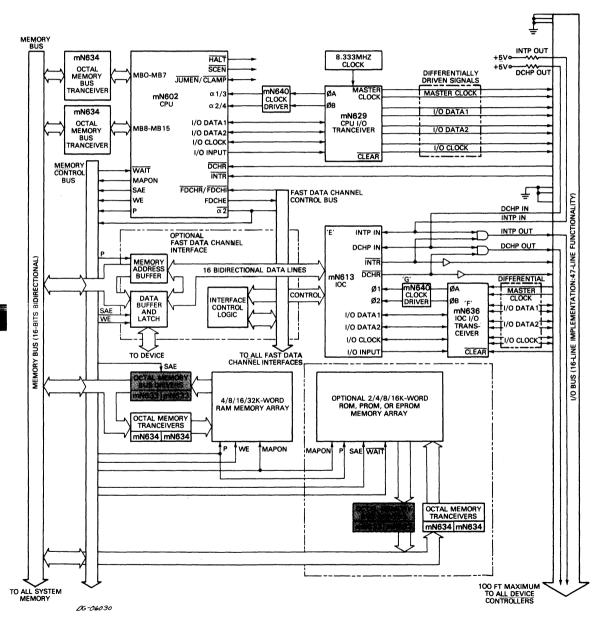

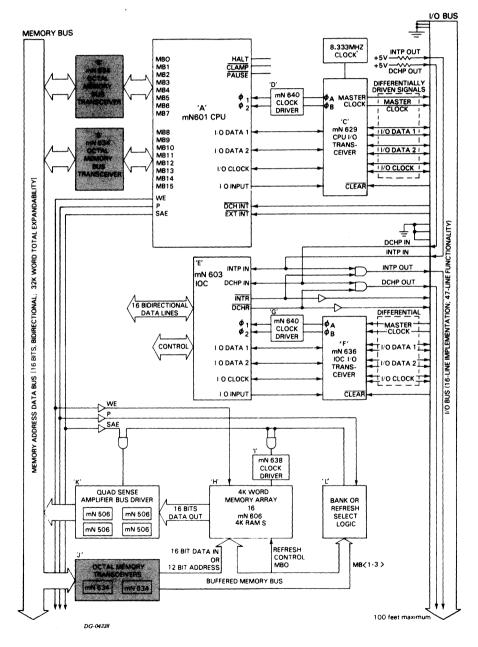

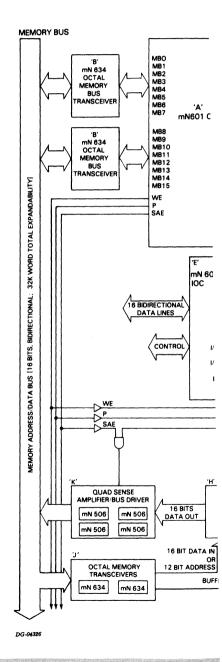

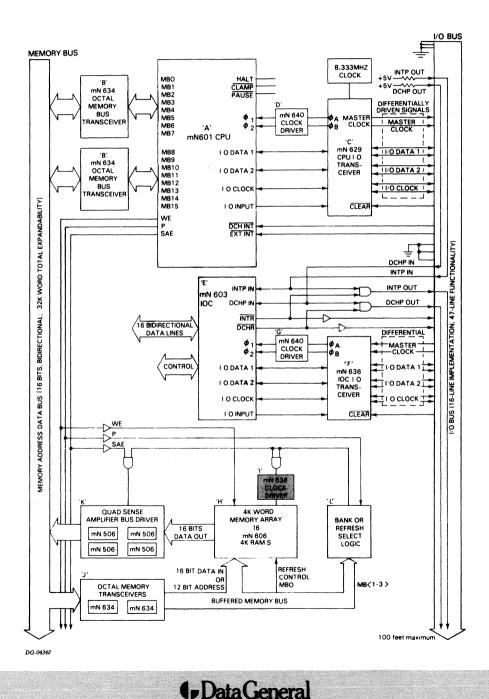

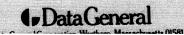

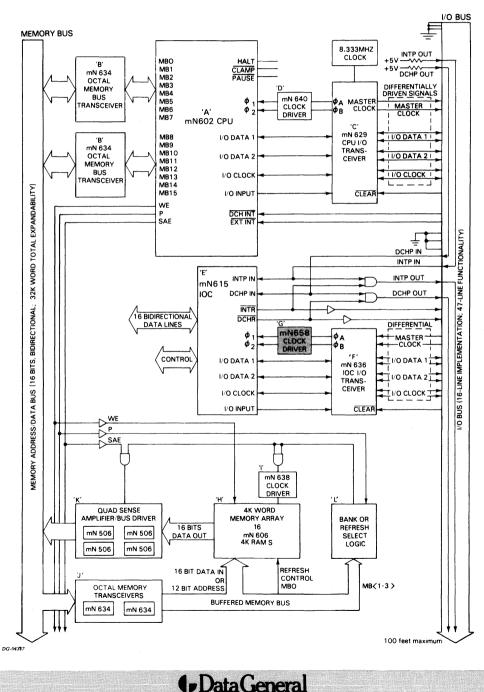

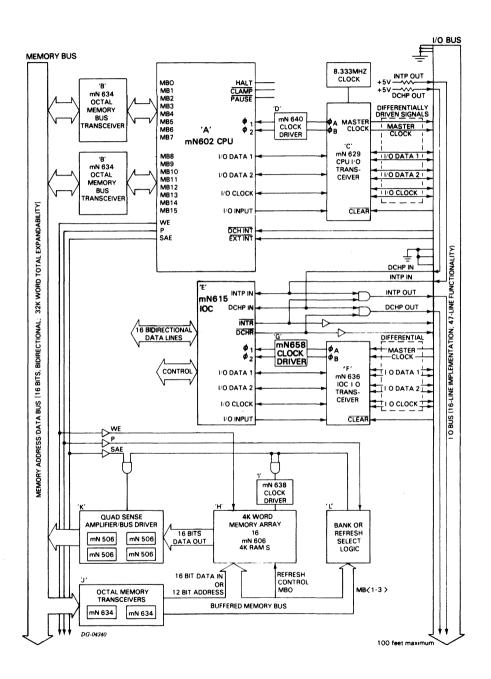

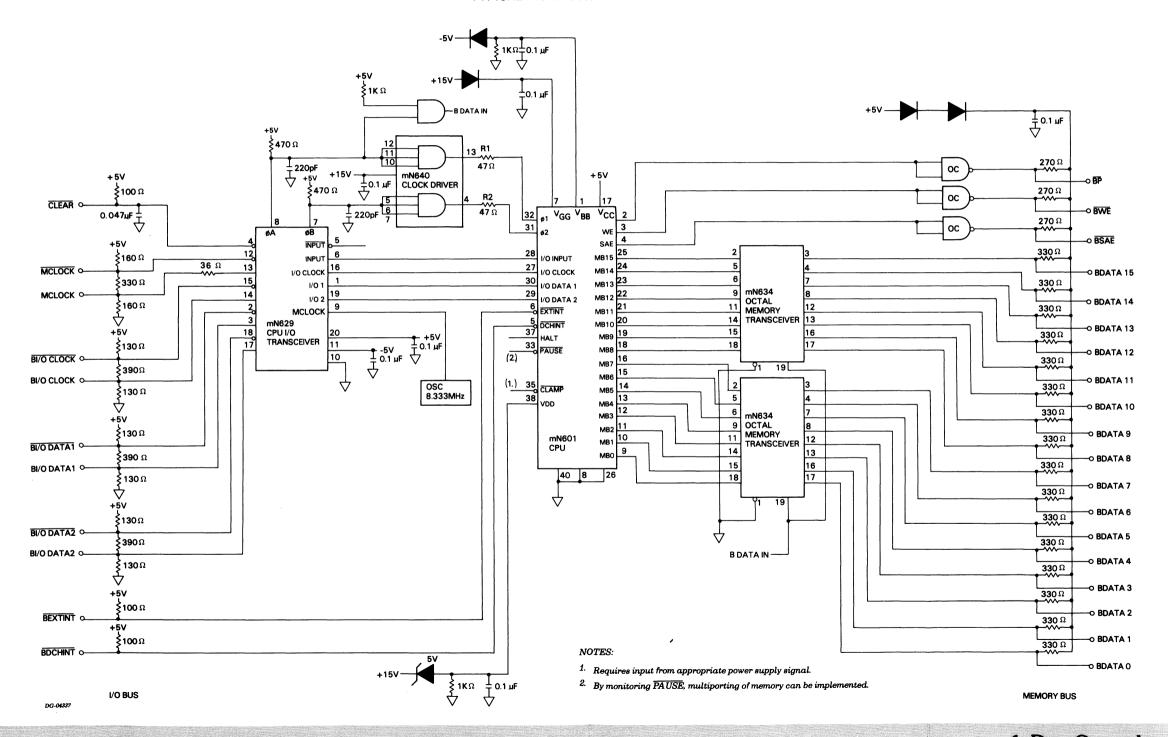

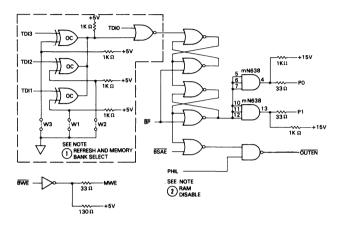

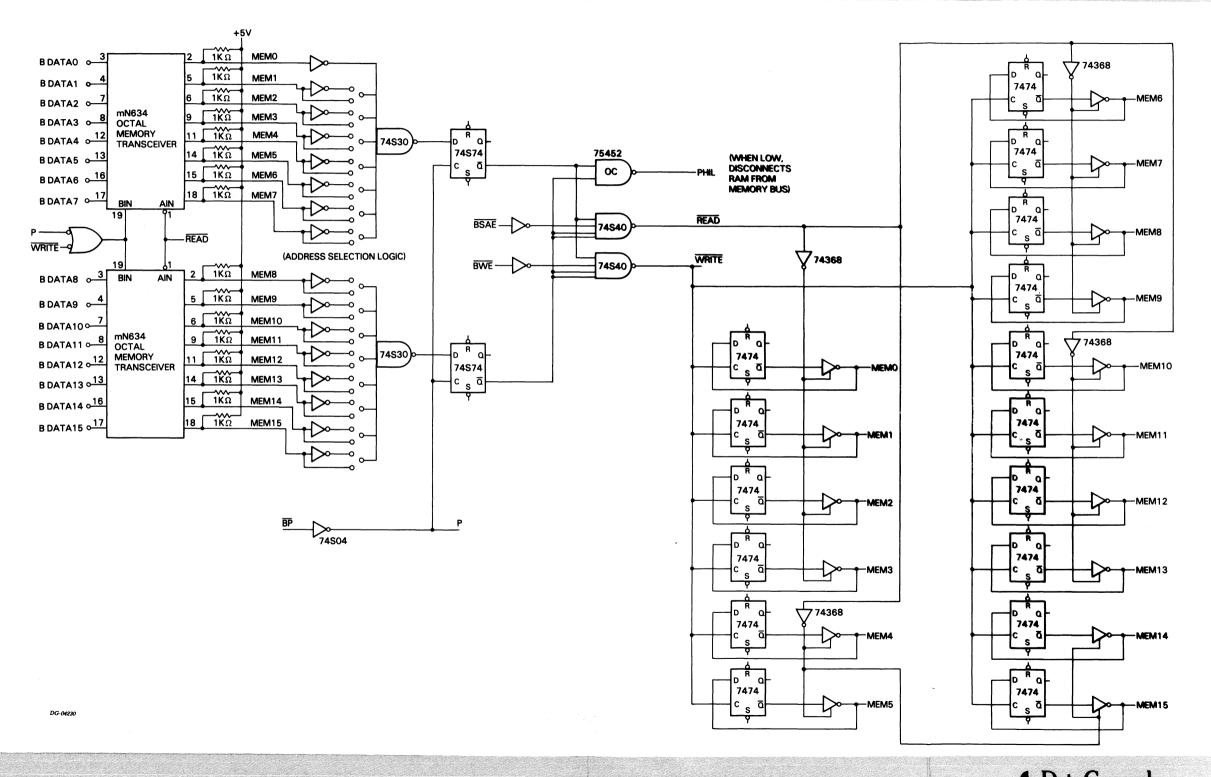

The block diagram on the opposite page shows a recommended mN602 microcomputer chip set configuration. It is organized around two data buses: memory and I/O (see diagram).

#### microNOVA MEMORY BUS

Memory addresses and data are passed between the mN601 or mN602 microprocessor and an array of mN606 RAMs via the microNOVA memory bus. This is a 16-bit parallel, bidirectional, high-speed bus.

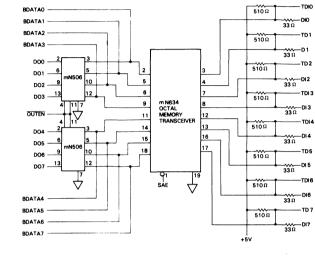

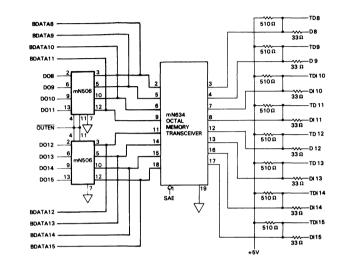

The microprocessor is interfaced to the bus via two mN634 octal memory transceivers. These transceivers drive data between the CPU's memory address/data lines and the memory bus.

A RAM grouping is interfaced to the bus via two mN634 octal memory transceivers and four mN506 quad sense amp/bus drivers. The memory transceivers drive both addresses and data sent to memory via the bus onto the RAM input lines while the sense amp/bus drivers drive data from the RAM output lines onto the bus.

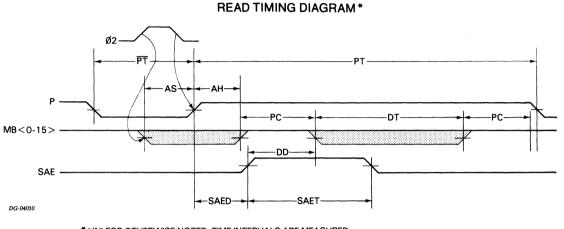

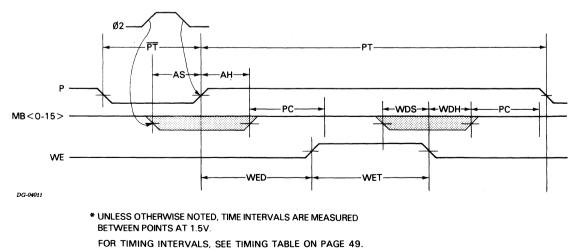

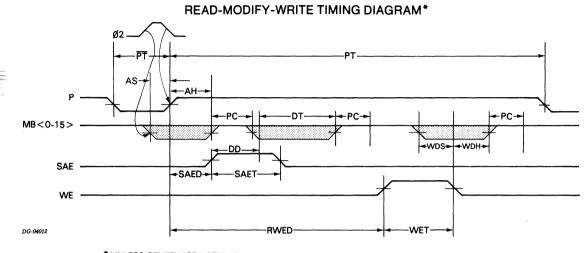

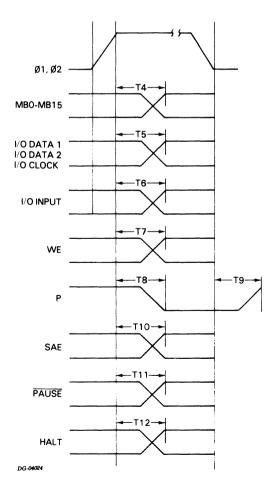

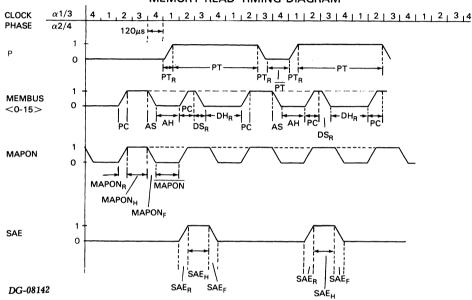

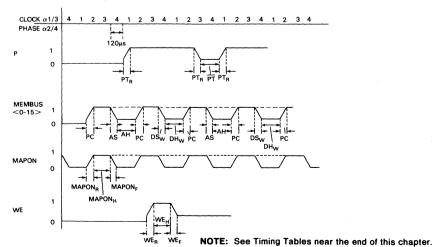

Three memory control lines, P, SAE and WE, allow the mN601 to perform four kinds of memory operations: read, write, read-modify-write and refresh.

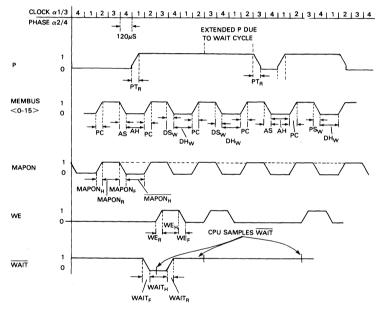

The mN602 contains the same 3 control lines, plus 2 additional ones, WAIT and MAPON. WAIT allows the CPU to extend memory operations to accomodate slow memories and MAPON allows the CPU to access a second 32K-word address space. The mN602 performs three kinds of memory operations: read, write, and refresh.

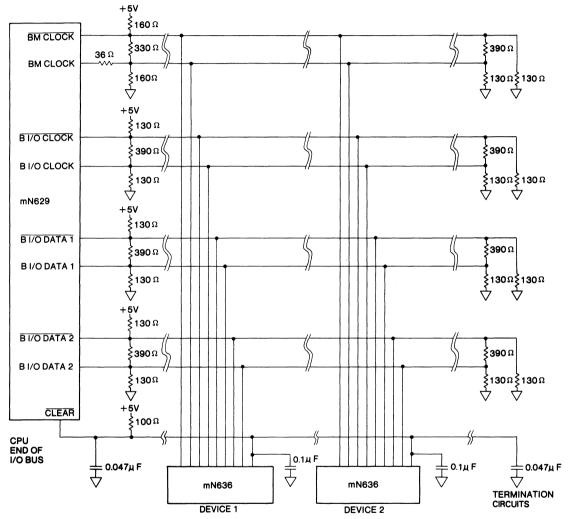

#### microNOVA I/O BUS

Information is passed between the microprocessor and the I/O controllers via the bidirectional, microNOVA I/O bus. This bus combines the advantages of high speed with high noise immunity (due to its differential nature, described below), while permitting the use of low cost ribbon cable. The I/O bus can be extended to a maximum distance of 100 feet from the microprocessor.

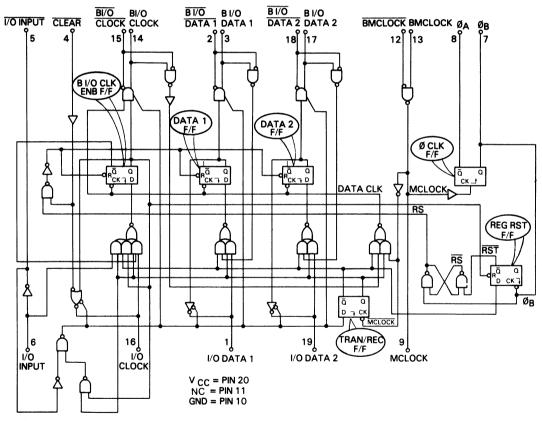

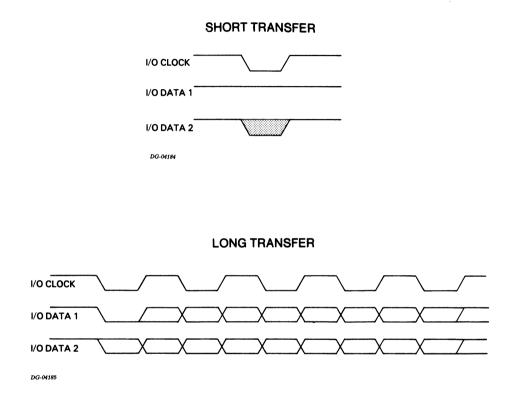

The microNOVA I/O bus contains 16 lines. The most critical lines (two serial data lines and two clock lines) are differentially driven and received by an mN629 CPU I/O transceiver and one mN636 IOC transceiver per I/O controller.

# **OVERVIEW**

At the microprocessor end of the bus, the CPU I/O transceiver receives serial data from the CPU and differentially drives it to the IOC I/O transceiver(s). It also receives the differentially driven data signals from the IOC I/O transceiver(s) and passes the data to the CPU. At the I/O controller end of the bus, each IOC I/O transceiver performs a similar function for its I/O controller. Up to twenty IOC I/O transceivers can be interfaced to the microNOVA I/O bus.

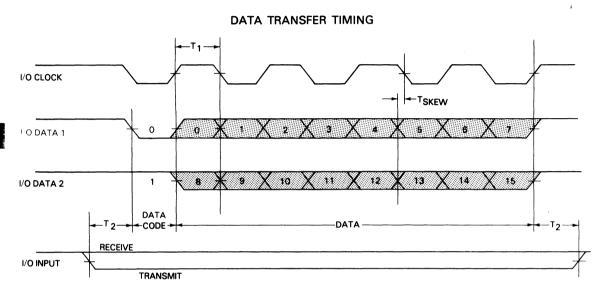

The differentially driven I/O CLOCK (see diagram) is transmitted with the data; it strobes the data into the receiving circuit. The CPU I/O transceiver differentially drives the MASTER CLOCK to all IOC I/O transceivers. Each IOC transceiver passes the MASTER CLOCK to its IOC as two non-overlapping clocks via an mN640 clock driver. The MASTER CLOCK synchronizes the operation of the I/O controllers with the CPU.

A system reset line (CLEAR), two device request lines, two types of device priority lines, and three ground lines comprise the remainder of the bus.

The CLEAR line allows the system to be reset by external hardware. When this line is pulled to a low logic level for a period of 10 usecs, the microcomputer is reset. This time period ensures that the CPU and IOC I/O transceivers are in receive mode; refer to the mN601, mN602, mN603/613/615, mN629 and mN636 circuit descriptions.

The device request lines (EXTINT and DCHINT for mN601, INTR and DCHR for mN602) allow I/O devices to request microprocessor service for the purpose of transferring data in either of two modes: programmed I/O or data channel break. These are explained later in the section entitled Data Transfers.

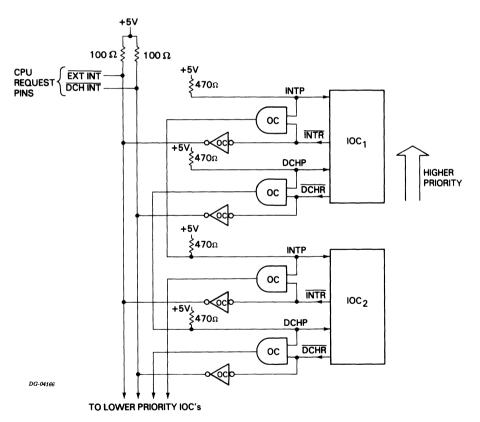

### Hardware Device Priority Network

The priority lines (INTP OUT, DCHP OUT, INTP IN and DCHP IN) comprise an interdevice daisy chain. When more than one I/O device is requesting service, this network gives priority to the device requesting service that is physically closest on the I/O bus to the microprocessor. The INTP lines control priority between devices requesting interrupt service. Similarly, the DCHP lines control priority between devices.

The manner in which the priority system is implemented is the same for both types of requests. When a device requests service, that device's INTP/DCHP OUT line goes to the low logic level. This removes priority from devices further away from the microprocessor, by pulling their INTP/DCHP IN lines to a low logic level. When the microprocessor acknowledges a request for service, a device can respond only if it is requesting service and its INTP/DCHP IN line is at a high logic level. If it is at a low logic level, it indicates that a higher priority device in the chain is requesting service. The priority lines previously disabled by the service request are reenabled when the responding device clears its request line.

### mN601 16-BIT MICROPROCESSOR

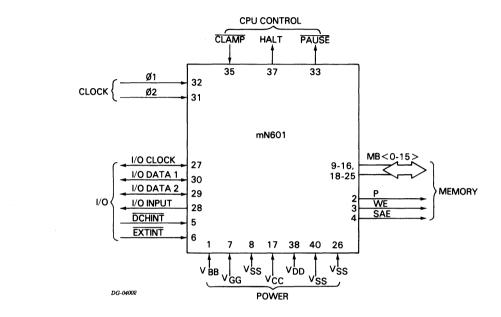

This is a 16-bit central processing unit (CPU) that incorporates the NOVA architecture. Its internal structure and operations are described in the mN601 section of this manual.

The mN601 is designed to operate with the following system buffer elements: two mN634 octal memory transceivers, an mN629 CPU I/O transceiver and an mN640 clock driver. The primary functions performed by these circuits for the CPU are described below. Detailed information is found in the individual circuit descriptions.

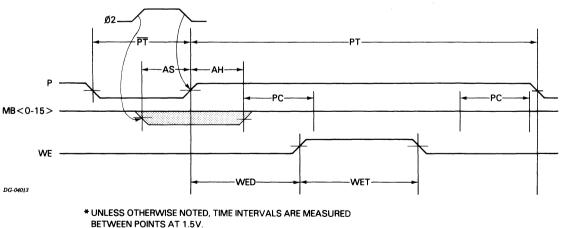

The CPU (designated 'A' in the diagram) has two ports: memory and I/O. Two mN634 octal memory transceivers (designated 'B') drive data between the CPU's memory address/data lines MB(..., 0-15...) and the microNOVA memory bus. The memory control signals, P, SAE and WE, allow the CPU to perform four kinds of memory operations: read, write, read-modify-write and refresh.

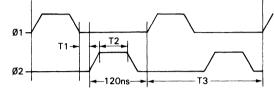

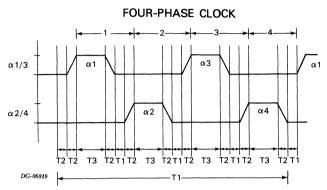

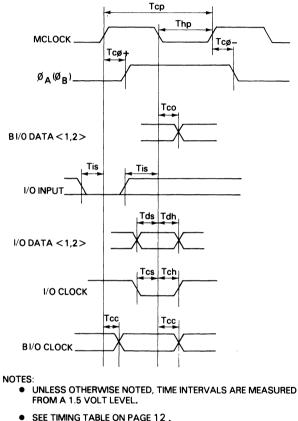

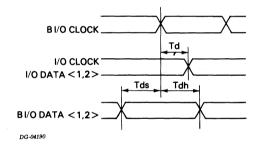

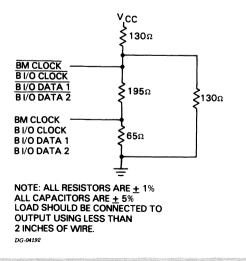

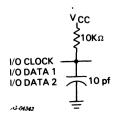

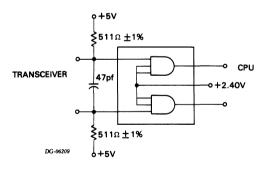

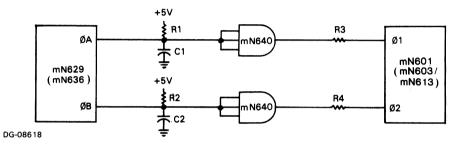

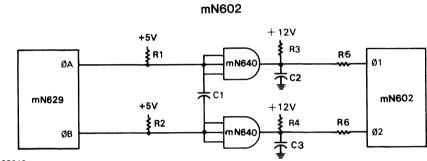

The mN629 CPU I/O transceiver (designated 'C') performs two functions for the CPU. First, it interfaces the CPU's serial data (I/O DATA <1,2>) and data clock (I/O CLOCK) lines with the microNOVA I/O bus. The I/O INPUT signal is used by the CPU to control the transceiver's operating mode, either transmit or receive. Second, the CPU I/O transceiver generates the two non-overlapping system clocks ( $\phi$ A and  $\phi$ B) from a single 8.333MHz clock input.

The  $\emptyset$  A and  $\emptyset$  B clocks are shaped by external circuitry (see Design Notes) and the outputs are supplied to the mN640 clock driver (designated 'D'). The clock driver receives these signals and provides signal characteristics that are compatible with the MOS clock input circuits of the CPU,  $\emptyset$  1 and  $\emptyset$  2.

The remaining mN601 pins perform the following functions. The HALT pin reflects the state of the CPU, halted (idling) or performing tasks. The PAUSE pin indicates when the CPU is performing a memory operation. By monitoring the output of this pin, multiporting of memory can be implemented. The CLAMP pin is an input pin used during the power-up and initialization sequence.

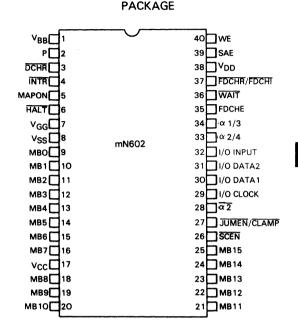

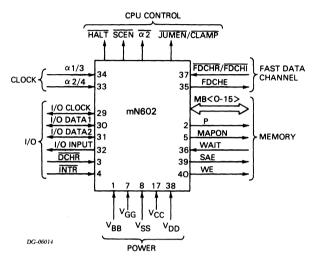

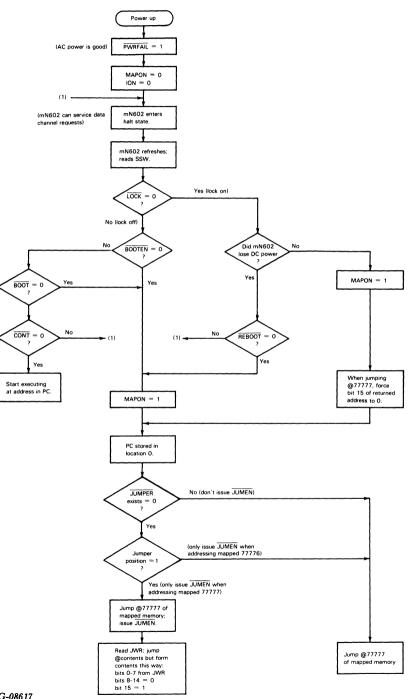

### mN602 16-BIT MICROPROCESSOR

The mN602 incorporates all the features of the mN601 CPU plus five new features.

The mN602 requires only standard TTL and MOS voltage levels of -5V, +5V and 12V. The CPU can use the mN603, the mN613, or the mN615 as an IOC.

The CPU can access memories with slow cycle times (EPROM memories) by sending additional SAE or WE signals to memory when WAIT goes low. A memory can cause the mN602 to wait a maximum of 50 CPU cycles, or  $24\mu$ sec.

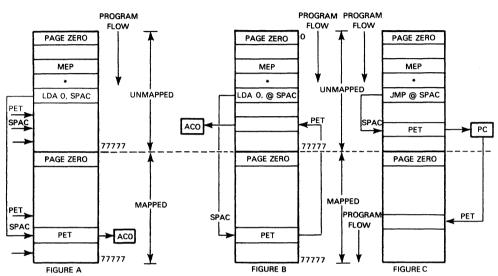

The mN602 can access up to 64K words of memory. This physical address space divides into two 32K-word logical address spaces that are addressable by the user. The MAPON flag determines which 32K-word bank of memory is addressed. When MAPON is 0, the lower (unmapped) bank is addressed. This is the address space available on mN601. When MAPON is 1, the upper (mapped) bank is addressed.

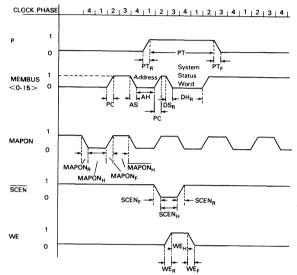

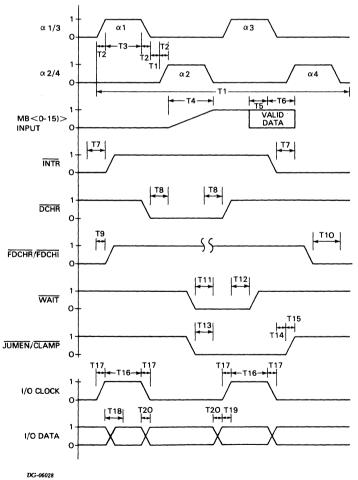

On memory refresh, the mN602 reads a System Status Word on the memory bus, during the data transfer phase. This word provides the CPU an external real-time clock, a set of non-maskable interrupts, and the state of the system the mN602 is part of (powerfail, etc.).

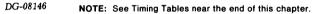

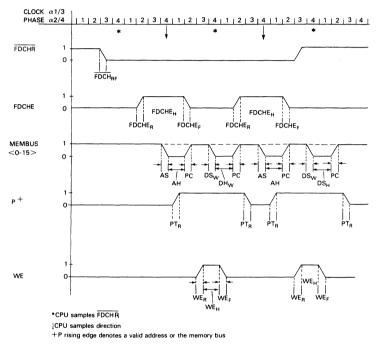

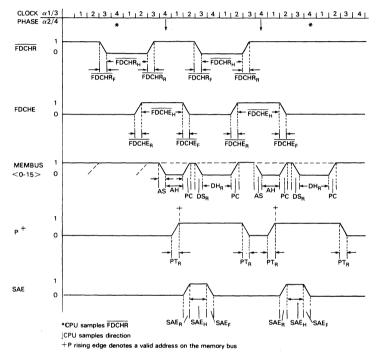

The last main feature of the mN602 is the integrated fast data channel. The FDCH makes direct memory accesses (DMAs) at 2 Mbytes/sec. The three control lines  $\overline{\alpha 2}$ , FDCHR/FDCHI, and FDCHE, handle all transactions between the CPU and the device. The clock signal  $\overline{\alpha 2}$  synchronizes high speed channel requests when FDCHR goes low. During the transfer, the CPU sends the needed memory control signals. Because of the transfer rate of the high speed data channel, the mN602 will not allow DMAs to slow memories.

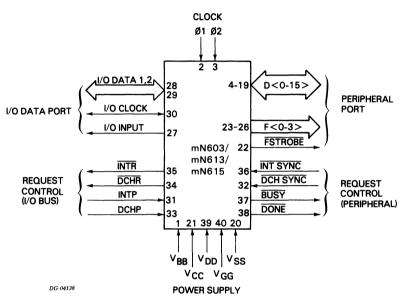

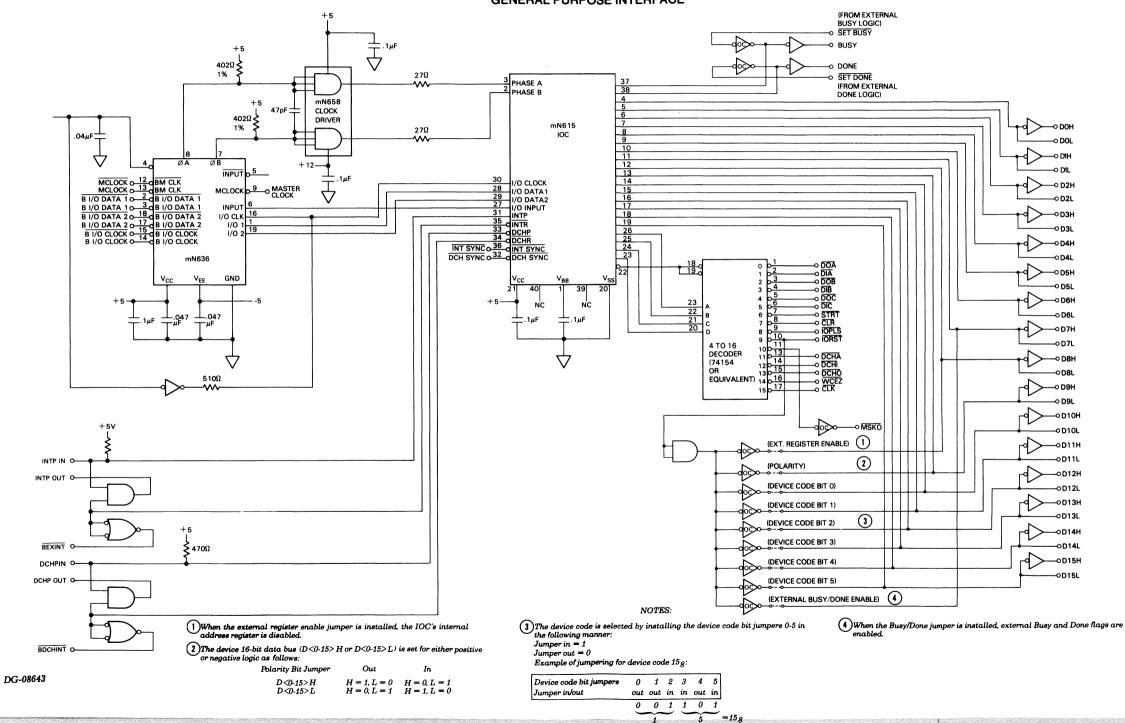

### mN603/613/615 I/O CONTROLLER (IOC)

The IOC is the interface between a peripheral device and the microNOVA I/O bus. Details of its internal architecture and operations are contained in the mN603/613/615 section of this manual.

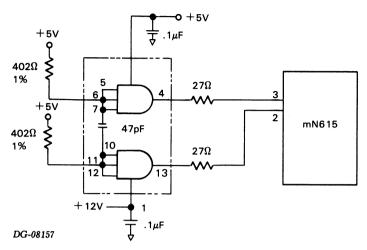

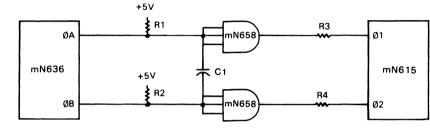

It is designed to operate with the following system buffer elements: an mN636 IOC I/O transceiver and a clock driver. The mN603 and mN613 operate with a mN640 clock driver. The mN615 uses a mN658 clock driver. The primary functions performed by these circuits for the IOC are described below. Detailed information is found in the individual circuit descriptions.

The IOC (designated 'E' in the diagram) has two ports: I/O bus and peripheral.

The mN636 IOC I/O transceiver (designated 'F') performs two functions for the IOC. First, it interfaces the IOC's serial data (I/O DATA<1,2>) and data clock (I/O CLOCK) lines with the microNOVA I/O bus. The I/O INPUT signal is used by the IOC to control the transceiver's operating mode, transmit or receive. Second, the mN636 transceiver receives the MASTER CLOCK from the I/O bus and generates two non-overlapping clock signals,  $\phi A$  and  $\phi B$ .

The  $\phi A$  and  $\phi B$  non-overlapping clocks are shaped by external circuitry (see Design Notes) and the outputs are supplied to the mN640 clock driver (designated 'G'). The clock driver receives these signals and provides signal characteristics that are compatible with the MOS clock input circuits of the IOC,  $\phi 1$  and  $\phi 2$ .

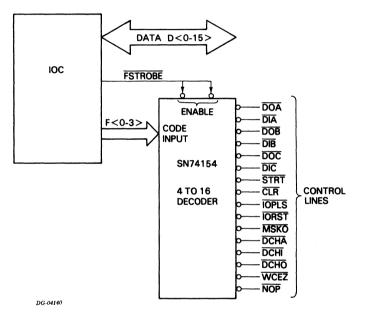

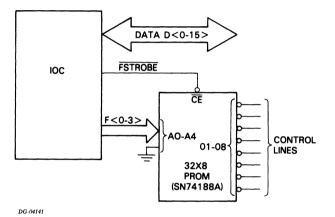

The IOC communicates with the device via a 16-bit parallel data bus and a group of control lines. The data and control lines together create the functional equivalent of the 47-line NOVA I/O bus.

5

# OVERVIEW

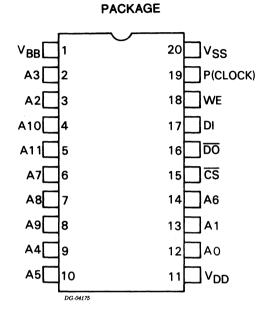

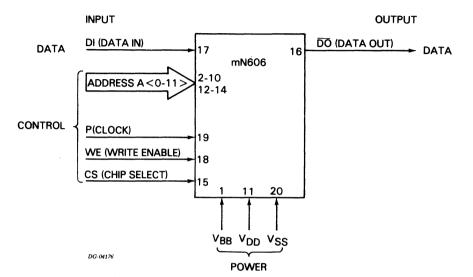

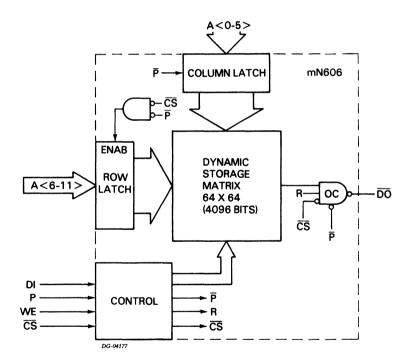

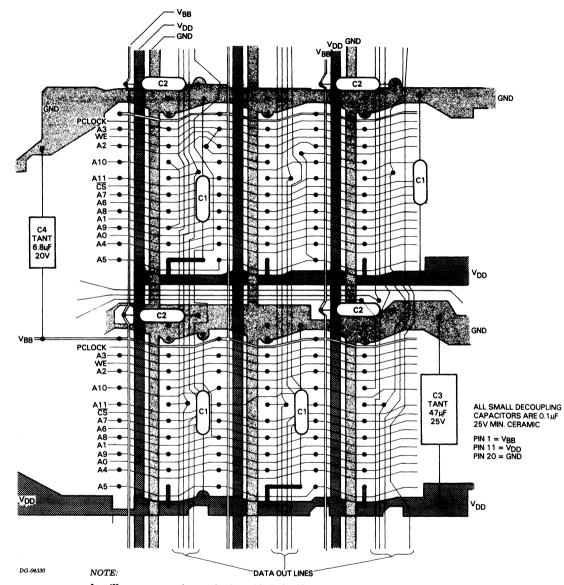

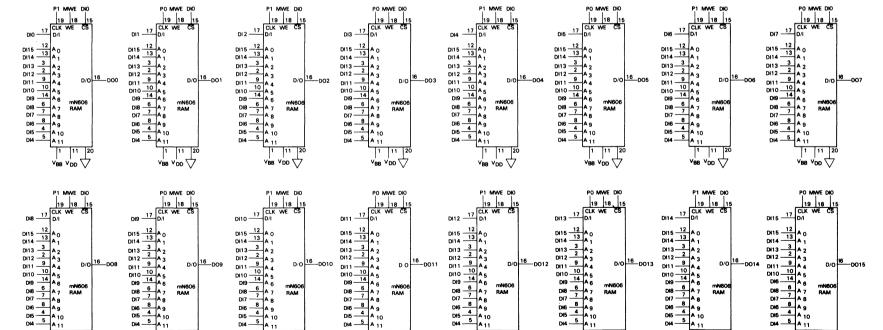

### mN606 4Kx1 DYNAMIC RAM

This is a 4096 by one bit memory. Details of its internal architecture and operations are contained in the mN606 section of this manual.

Sixteen mN606 RAMs comprise a 4Kx16-bit memory array. This array is designed to operate with the following system buffer elements: one mN638 clock driver, two mN634 octal memory transceivers and four mN506 quad sense amp/bus drivers. For an 8Kx16-bit array, it is necessary to add only one mN638 clock driver, since the two mN634 transceivers and four mN506 sense amp/bus drivers support 8K of memory. The primary functions performed by these system buffer elements for the mN606 RAMs are described below. Detailed information is found in the individual circuit descriptions.

The 4Kx16-bit dynamic RAM array (designated 'H' in the diagram) has two ports: input (address and data) and output.

The two mN634 octal memory transceivers (designated 'J') drive addresses and data from the microNOVA memory bus onto the RAM address and data input lines. The four mN506 quad sense amp/bus drivers (designated 'K') drive data from the RAM output lines onto the microNOVA memory bus.

The mN601 addresses up to 32,768 memory locations; thus, eight 4Kx16-bit memory arrays can be interfaced to the microNOVA memory bus. The mN602 addresses up to 65,536 memory locations; thus, 16 4Kx16-bit memory arrays can be interfaced to the microNOVA memory bus. Each 4Kx16-bit array has a 12-bit memory address (MB<4-15>). The external bank select logic (designated 'L') selects the appropriate array from the address appearing on the MB<1-3> lines.

When both the memory control signal P is asserted and the bank select logic is enabled, the mN638 clock driver (designated 'I') provides the signal characteristics required for the MOS clock input circuit of the RAM.

At the beginning of a memory operation, the RAM samples the address and tests the logic level, high or low, of MB0. If MB0 is at a high level, the RAM initiates a refresh operation; if it is at a low level, the RAM initiates either a read, write, or read-modify-write operation.

When mN606 dynamic RAMs are used in a microNOVA-based system, the mN601 microprocessor automatically refreshes them without external circuitry.

## DATA TRANSFERS

Addresses and data are transferred between the CPU and memory via the microNOVA memory bus. Control information and data words are transferred between the CPU and I/O devices via the microNOVA I/O bus.

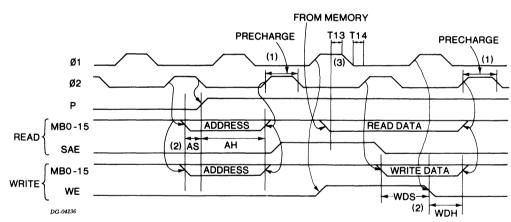

### MEMORY

The microprocessors perform three kinds of memory operations: read, write, and refresh. All memory operations are initiated on the rising edge of P. As described above, the address on the bus is sampled by the memories and the state of MB0 is tested. If this signal is high, a refresh operation is performed; if it is low, either a read, write, or read-modify-write operation is performed. Detailed information is found in the Memory Operations section of the mN601 and mN602 circuit description.

When non-volatile memory is required, programmable read-only memory (PROM) can be used. Refer to the microNOVA Computer Systems Technical Reference (DGC ordering number 014-000073). At the board level, PROM can overlay RAM, and PROM priority control lines resolve any memory conflicts in favor of the PROM.

### **INPUT/OUTPUT**

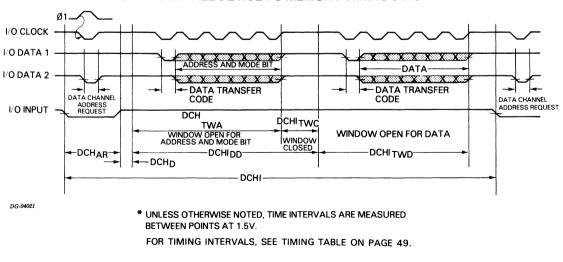

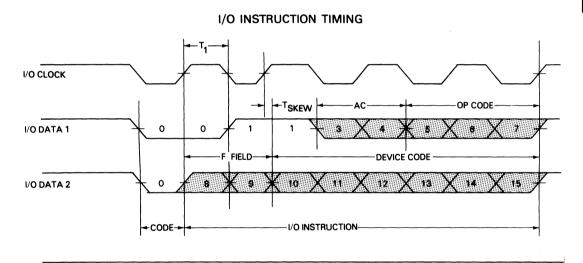

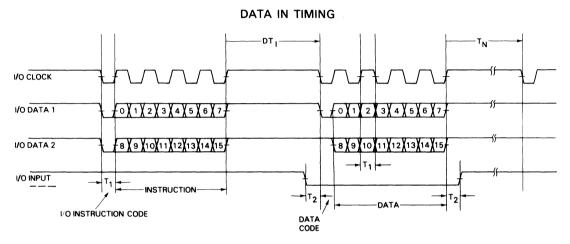

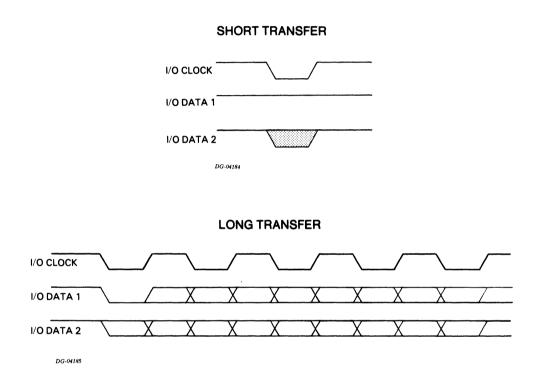

Information is passed between the CPU and I/O controllers via the two serial data lines of the microNOVA I/O bus. The bus connections are made through the appropriate I/O transceivers. The data consists of both control information and 16-bit data words.

The CPU performs I/O data transfers under two operating modes: programmed I/O and data channel break. Under programmed I/O, the CPU moves data betweeen one of its internal registers (namely, accumulators; see the mN601 and mN602 sections) and an I/O device. Under data channel break, the CPU moves data between memory and an I/O device. Data channel breaks allow blocks of information to be transferred without altering program flow. In addition, data channel breaks are transparent to the executing program.

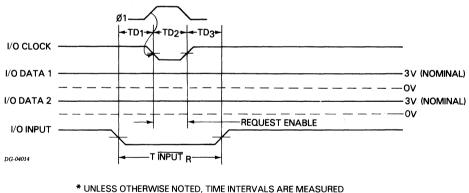

An I/O device requests microprocessor service for the purpose of transferring data by asserting either the program interrupt or data channel break device request lines. These requests are synchronized by a CPU-generated signal called Request Enable. It ensures that the device request and priority lines are at a steady state when they are examined by the CPU. Request Enable is sent to all I/O controllers connected to the I/O bus as a two-bit code (11), one bit carried on each serial data line.

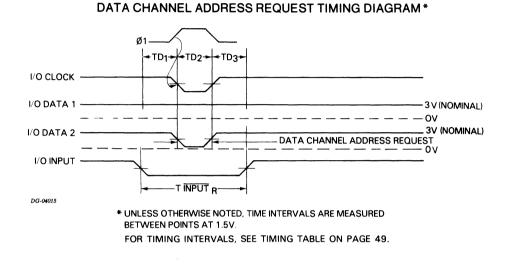

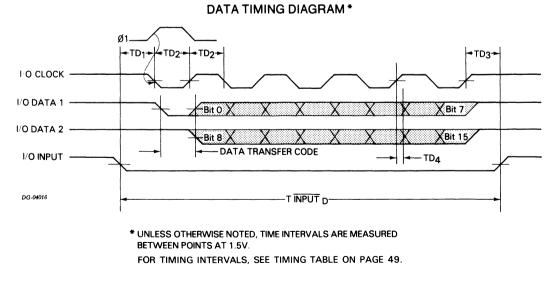

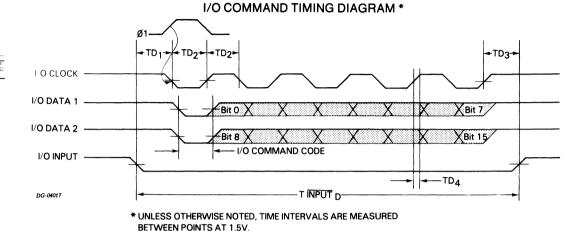

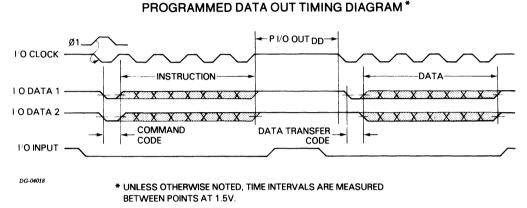

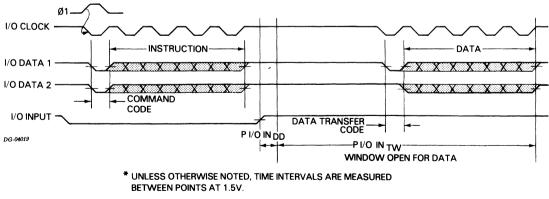

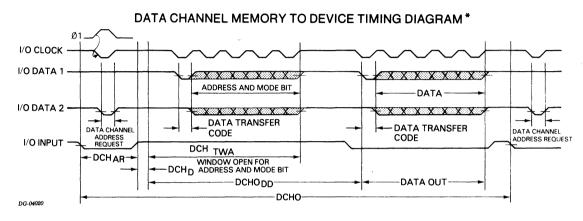

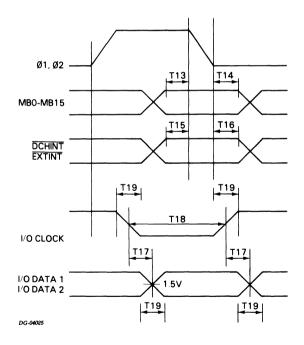

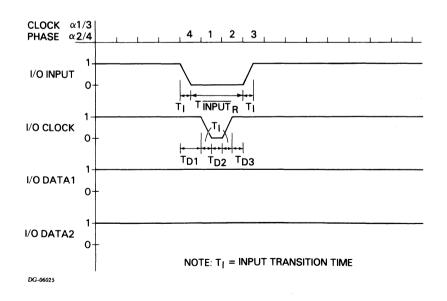

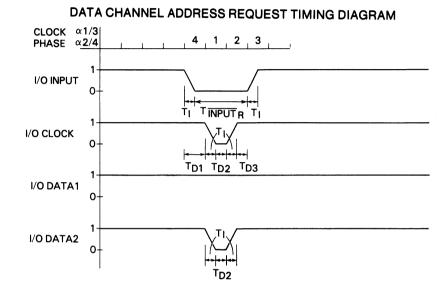

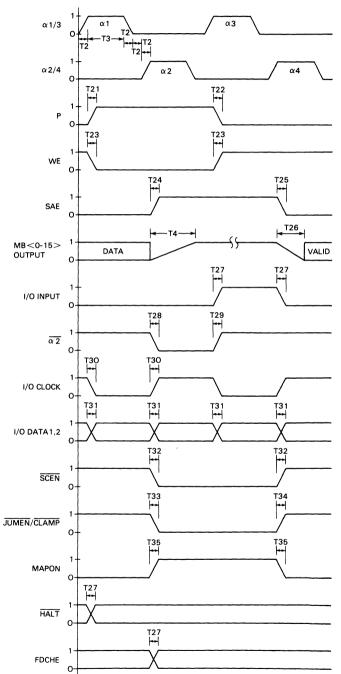

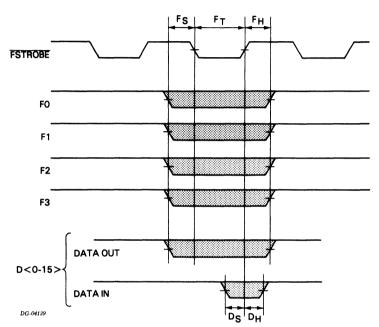

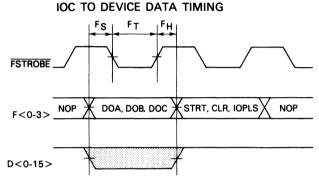

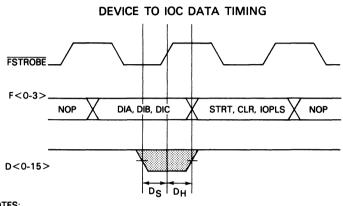

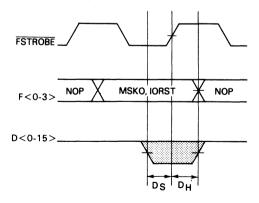

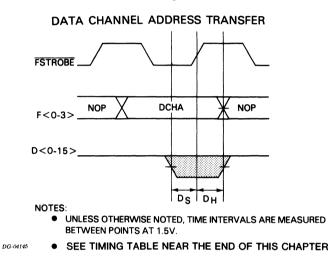

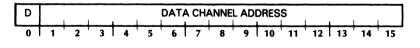

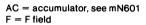

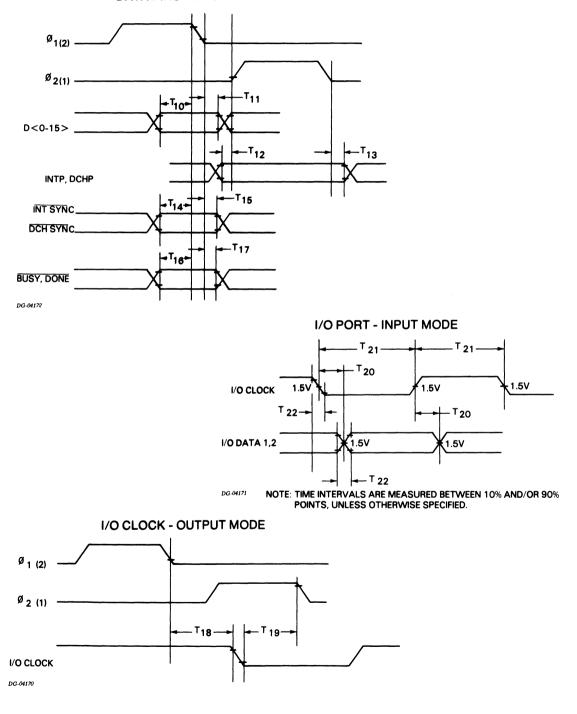

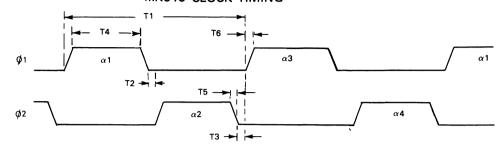

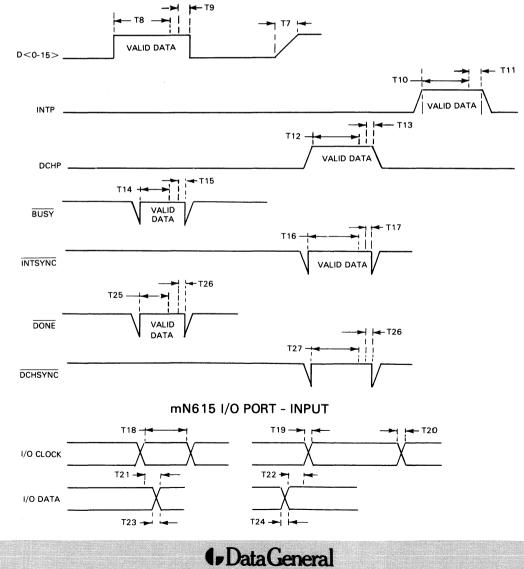

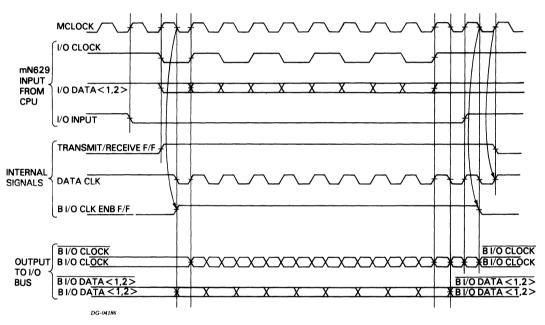

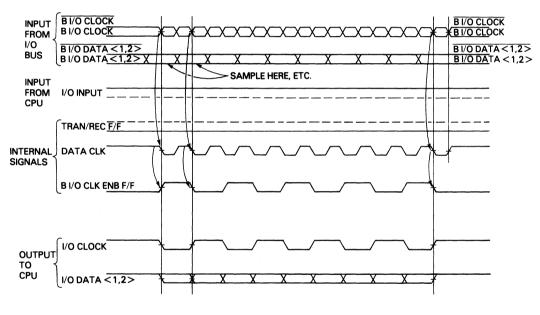

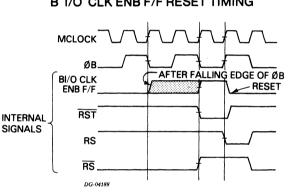

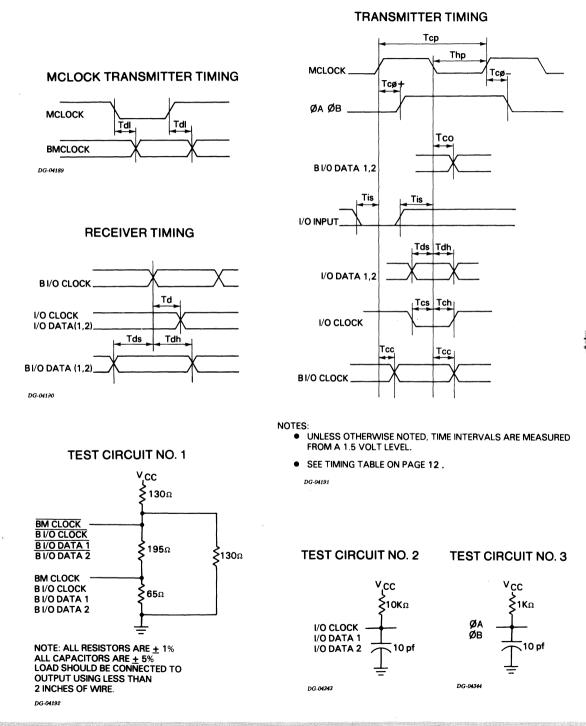

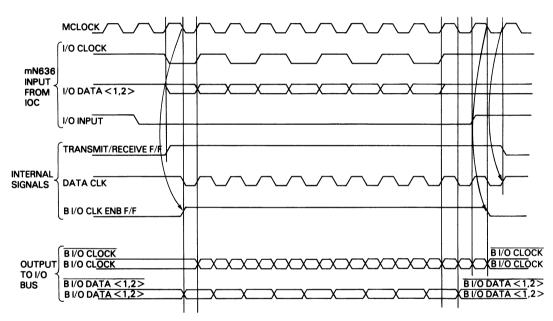

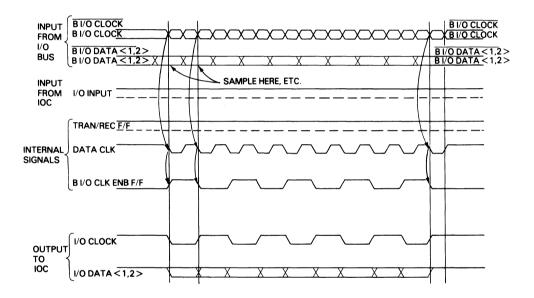

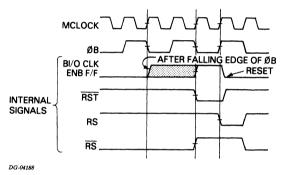

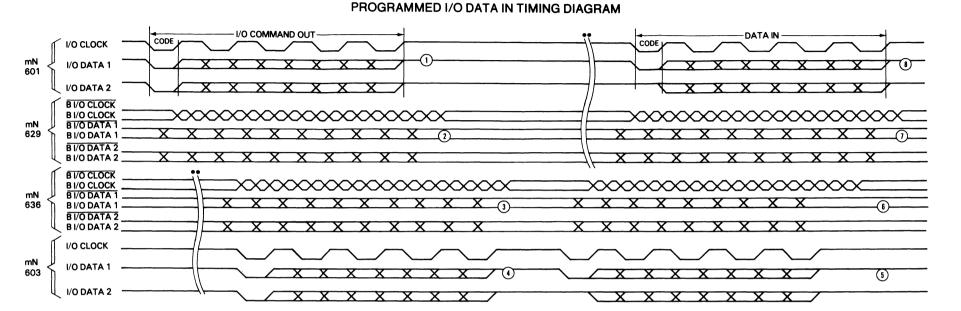

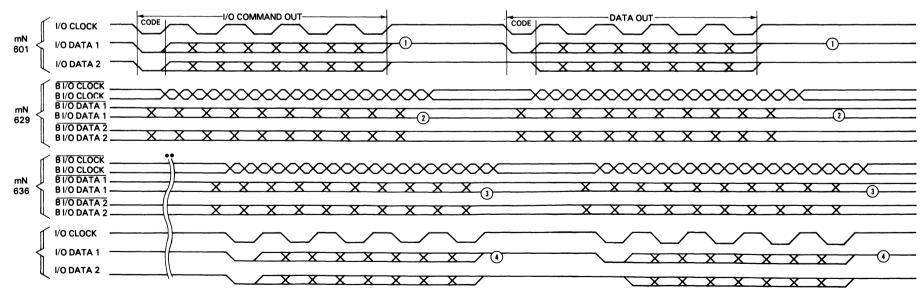

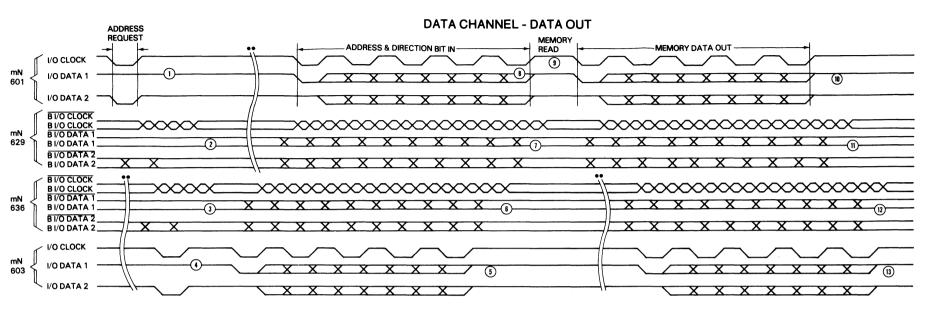

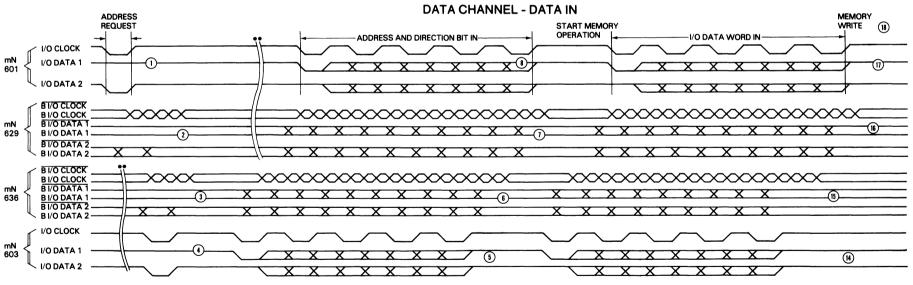

Detailed information concerning I/O data transfers is found in the I/O Operations sections of the mN601 and mN602 circuit descriptions and in the mN603/613/615, mN629 and mN636 circuit descriptions. Timing diagrams of I/O bus operations can be seen in Appendix A. These diagrams depict the transmission and reception of control information and data words as they pass between the CPU, the CPU transceiver, the IOC transceiver and the I/O controller, under both programmed I/O and data channel. (The I/O transactions appearing in the diagrams apply when the system is configured as shown in the block diagram at the beginning of this section.)

#### Programmed I/O

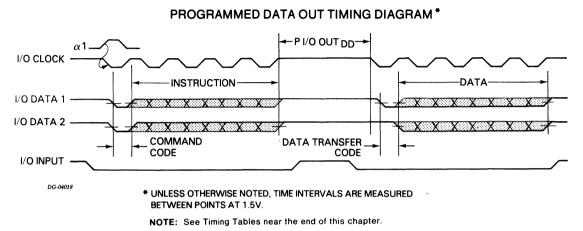

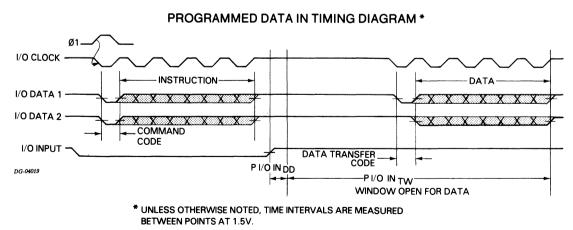

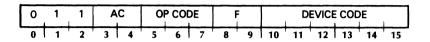

Under programmed I/O, the CPU sends the I/O instruction, exactly as fetched from memory, to all controllers connected to the microNOVA I/O bus. The instruction includes information that identifies the controller to which it is directed. Following the instruction, the CPU performs either a data out operation or a data in operation, as required by the instruction.

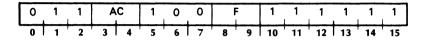

When either data out or data in instructions are performed, both the instruction and the 16-bit data word are transmitted as 18-bits, 9 bits on each line. The first bit on each line comprises a two-bit code that identifies the type of transfer; 00 indicates an I/O command and 01 indicates a data word.

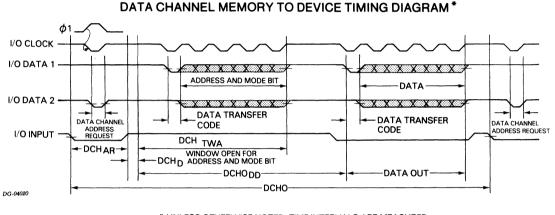

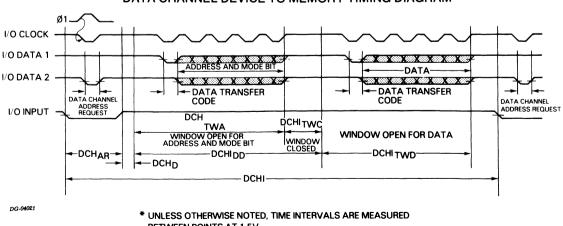

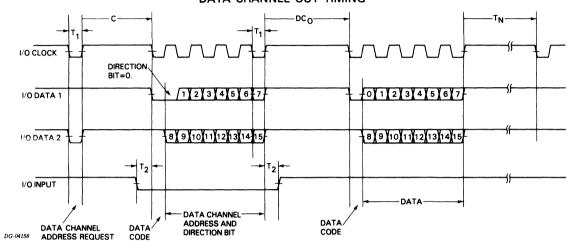

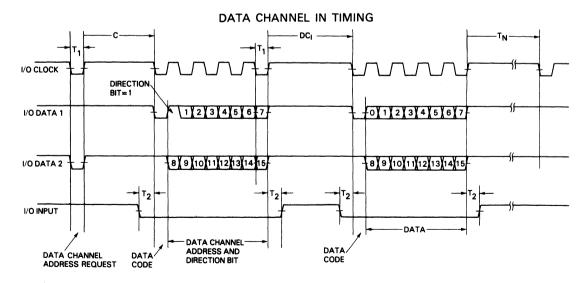

#### Data Channel Break (Standard Data Channel)

When the CPU performs a data channel break, it sends an address request to the microNOVA I/O bus. This request consists of a two-bit code (10). The highest priority device requesting data channel service responds to this code. The device responds first by sending a 16-bit word (plus the two-bit data word prefix code, 01, described above) containing a 15-bit memory address and a direction of transfer bit (data out or data in) to the CPU. Following the receipt of this information, the CPU initiates a memory operation at the address specified; then, it examines the direction of transfer bit.

If it is set for a data out, the CPU transmits the 16-bit word received during the read portion of the memory operation together with the two-bit data word prefix code. The memory operation is terminated without altering the contents of the addressed location.

If it is set for a data in, the device transmits the 16-bit word to be entered in memory together with the two-bit data word prefix code. After the data word is received by the CPU, it is written into memory during the write portion of the memory operation in progress.

## **RELATED DOCUMENTS**

The following supporting documents are available from Data General Corporation.

| Document                                                      | Ordering No. |

|---------------------------------------------------------------|--------------|

| microNOVA Programmer's Reference                              | 015-000050   |

| microNOVA DTOS                                                | 015-000059   |

| microNOVA Computer Systems                                    | 014-000073   |

| Microproducts Hardware<br>Reference Series                    |              |

| MP / 100 Computer System                                      | 014-000668   |

| MP/200 Computer System                                        | 014-000667   |

| Input/Output and Interfacing                                  | 014-000665   |

| Communications Interfaces and<br>Character Device Controllers | 014-000660   |

| Disk and Diskette Drives                                      | 014-000661   |

| Magnetic Tape Transport                                       | 014-000664   |

| Sensor I/O                                                    | 014-000659   |

|                                                               |              |

7

**OVERVIEW**

# mN601 16-BIT MICROPROCESSOR CONTENTS

mN601 CONTENTS

2

| 1  | FEATURES                                        |

|----|-------------------------------------------------|

| 1  | GENERAL DESCRIPTION                             |

| 2  | PIN DESCRIPTIONS                                |

| 4  | ARCHITECTURE                                    |

| 6  | INTRODUCTION TO INSTRUCTION SET                 |

| 7  | MEMORY REFERENCE INSTRUCTIONS                   |

| 7  | ADDRESSING MODES                                |

| 8  | Indirect Addressing                             |

| 9  | Auto-Incrementing/Decrementing                  |

| 11 | NO ACCUMULATOR-EFFECTIVE ADDRESS INSTRUCTIONS   |

| 11 | ONE ACCUMULATOR-EFFECTIVE ADDRESS INSTRUCTIONS  |

|    |                                                 |

| 12 | TRAP INSTRUCTION                                |

| 13 | ARITHMETIC/LOGICAL INSTRUCTIONS                 |

| 15 | TWO ACCUMULATOR-MULTIPLE OPERATION INSTRUCTIONS |

| 17 | MULTIPLY/DIVIDE INSTRUCTIONS                    |

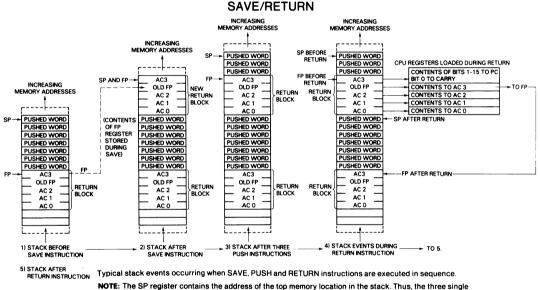

| 18 | STACK INSTRUCTIONS                              |

| 23 | INPUT/OUTPUT INSTRUCTIONS                       |

| 23 | BUSY AND DONE FLAGS                             |

| 23 | ADDRESSING NON-EXISTENT DEVICE CODES            |

| 26 | PROGRAM INTERRUPTS                              |

| 26 | 16-LEVEL PRIORITY INTERRUPTS                    |

| 20 |                                                 |

| 27 | CPU I/O INSTRUCTIONS                            |

| 32 | MEMORY OPERATIONS                               |

| 32 | ADDRESS DATA PINS                               |

| 32 | CONTROL                                         |

| 33 | READ OPERATION                                  |

| 33 | WRITE OPERATION                                 |

| 34 | READ-MODIFY-WRITE OPERATION                     |

| 34 | REFRESH OPERATION                               |

# mN601 CONTENTS

2

ij

| 35 | I/O OPERATIONS               |

|----|------------------------------|

| 35 | PROGRAMMED I/O               |

| 35 | DATA CHANNEL BREAK           |

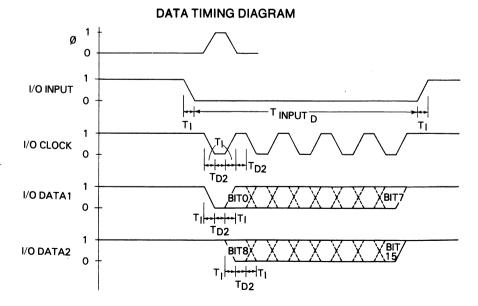

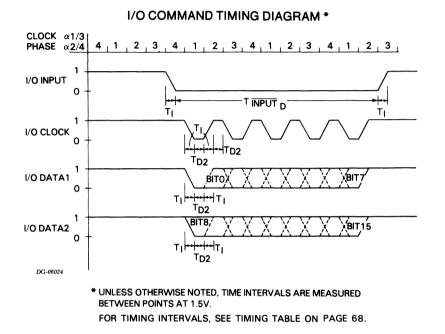

| 35 | I/O BUS TRANSFERS            |

| 36 | REQUEST ENABLE               |

| 37 | DATA CHANNEL ADDRESS REQUEST |

| 37 | DATA                         |

| 38 | I/O COMMAND                  |

| 39 | I/O TRANSFER PROTOCOL        |

| 39 | Programmed I/O Data Out      |

| 39 | Programmed I/O Data In       |

| 40 | Data Channel Data Out        |

| 40 | Data Channel Data In         |

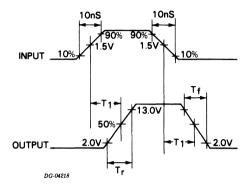

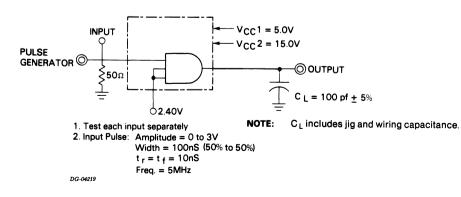

| 41 | TIMING                       |

| 41 | Programmed I/O Latency       |

| 42 | Data Channel Latency         |

| 43 | STATUS                       |

| 43 | INITIALIZATION               |

| 43 | HALT                         |

| 43 | RESET                        |

| 43 | INSTRUCTION EXECUTION TIMES  |

|    |                              |

| 45 | ELECTRICAL SPECIFICATIONS    |

| 49 | TIMING TABLES                |

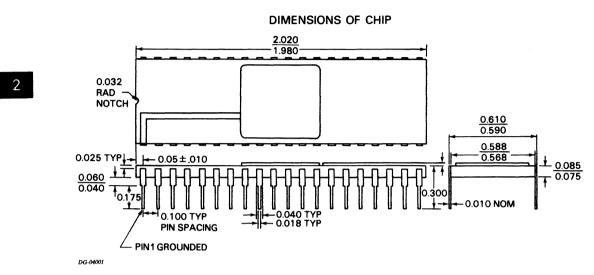

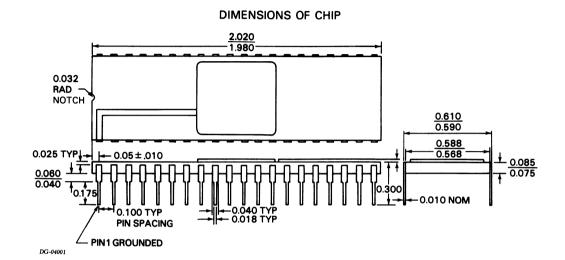

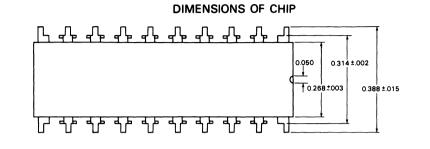

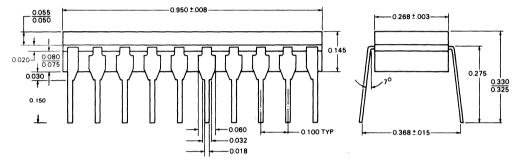

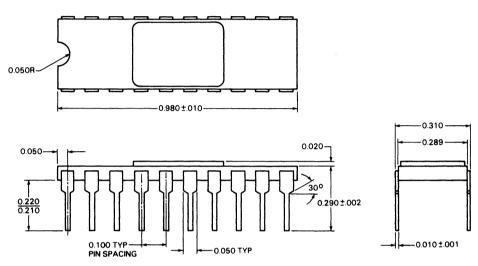

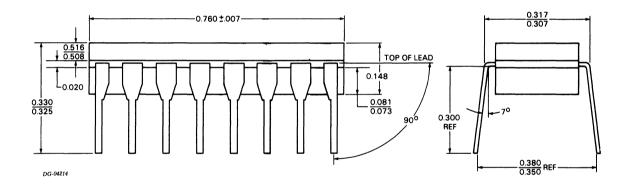

| 50 | PACKAGE SPECIFICATIONS       |

# mN601 16-BIT MICROPROCESSOR

Data General Corporation, Westboro, Massachusetts 01581

## **16-BIT MICROPROCESSOR (CPU) NMOS INTEGRATED CIRCUIT**

### FEATURES

- FULL NOVA 16-BIT ARCHITECTURE AND INSTRUCTION SET IN A SINGLE 40-PIN NMOS SILICON-GATE CHIP

- INTEGRAL DATA CHANNEL, REAL-TIME CLOCK, AND MULTIPLY/DIVIDE

- INTEGRAL HIDDEN REFRESH AND CONTROL LOGIC FOR DYNAMIC RAMS

- COMPREHENSIVE STACK ARCHITECTURE WITH HARDWARE STACK AND FRAME POINTER REGISTERS

- POWERFUL SAVE AND RETURN INSTRUCTIONS FOR SUBROUTINE CALLS

- MULTIPLE ACCUMULATORS

- SYSTEM MEMORY SUPPORT UP TO 32K WORDS OF RAM/PROM

- SINGLE WORD INSTRUCTION FORMAT IN A VARIETY OF ADDRESSING MODES - ABSOLUTE, RELATIVE, INDEXED, DEFERRED AND AUTO-INCREMENT/ DECREMENT

- SEPARATE MEMORY AND I/O BUSES

- I/O BUS PROVIDES FUNCTIONAL EQUIVALENT OF 47-LINE NOVA I/O BUS

- 16-LEVEL PROGRAMMED PRIORITY INTERRUPT

## **GENERAL DESCRIPTION**

The mN601 is a full 16-bit NMOS microprocessor that provides the central processing function for Data General's microNOVA family. The mN601 features NOVA 16-bit architecture, including hardware multiply/divide; multiple addressing modes, including absolute, relative, indexed, deferred, and auto-increment/decrement; multiple accumulators, including two that can be used as index registers; hardware stack and frame pointers with stack overflow protection; programmed priority interrupt to 16 levels; and separate memory and I/O buses.

Data General's microNOVA family of integrated circuits also includes memories, peripheral controllers, and supporting circuits which can be used to develop a complete, high-performance, microcomputer system.

The mN601 is supported by the mN606 4K RAM, the mN603 I/O Controller (IOC), and system buffer elements. The 4096-bit mN606 uses cost- effective dynamic NMOS RAM technology to support microNOVA's large memory orientation. The mN603 IOC delivers the full functional capability of the 47-line NOVA I/O bus, including a parallel 16-bit I/O port. System buffer elements allow microNOVA support up to 32K words of memory and a full complement of peripherals.

Data General Corporation, Westboro, Massachusetts 01581

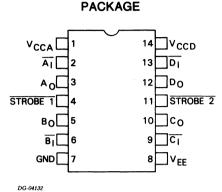

PACKAGE

**mN601**

DG-04026

## **PIN DESCRIPTIONS**

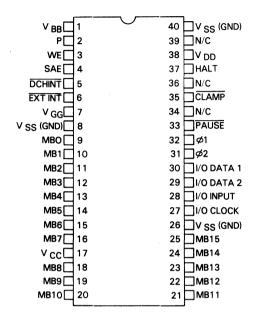

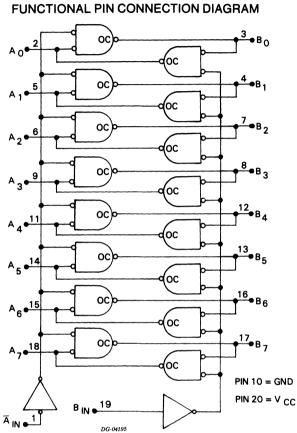

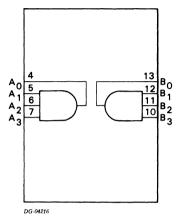

• The diagram below shows the pin connections, and the table describes the function of each pin shown in the diagram.

## FUNCTIONAL PIN CONNECTION DIAGRAM

### PIN FUNCTIONS

| MNEMONIC | PIN<br>NO.    | I/O      | FUNCTION                                                                                                                                                                                                                                                                                                      |

|----------|---------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          |               |          | СГОСК                                                                                                                                                                                                                                                                                                         |

| φ1<br>φ2 | 32<br>31      | IN<br>IN | Two-phase system clock. Operates between 0 and 14V amplitude. Generates 4-phase internal clock, providing internal control timing.                                                                                                                                                                            |

|          |               |          | MEMORY BUS                                                                                                                                                                                                                                                                                                    |

| MB0-MB15 | 9-16<br>18-25 | 1/0      | Bi-directional, data and address bus. When used as a data bus, MB0 contains the MSB (most significant bit) and MB15, the LSB (least significant bit). As an address bus, MB<1-15>contains the address and MB0 defines the memory operation as either refresh or read/write.                                   |

|          |               |          | This bus is precharged internally by the CPU. It is held high by individual internal pull-up resistors tied to each line. During address or data transfers, each line transmitting a 0 is discharged; each line transmitting a 1 is undischarged. See the Memory Operations Section for detailed information. |

|          |               |          | MEMORY CONTROL                                                                                                                                                                                                                                                                                                |

| Р        | 2             | Ουτ      | Active high. Initiates all memory cycles. When P goes high, indicates a valid address is on the memory bus.                                                                                                                                                                                                   |

| SAE      | 4             | Ουτ      | Active high. Enables sense amplifier outputs on the memory bus during a read operation.                                                                                                                                                                                                                       |

| WE       | 3             | OUT      | Active high. Enables write operation. On the falling edge of WE, information on the memory bus is written into memory.                                                                                                                                                                                        |

**mN601**

**PIN DESCRIPTIONS**

# mN601 PIN DESCRIPTIONS

### **PIN FUNCTIONS**

| MNEMONIC                           | PIN<br>NO.   | I/O        | FUNCTION                                                                                                                                                                                                                                                                                     |

|------------------------------------|--------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                    |              |            | I/O BUS                                                                                                                                                                                                                                                                                      |

| I/O DATA 1<br>I/O DATA 2           | 30<br>29     | 1/0<br>1/0 | Two-line, bi-directional bus. All data and I/O command information is transmitted serially<br>between the mN601 and I/O devices at the MASTER CLOCK rate. During a 16-bit<br>transfer, I/O DATA1 carries the most significant 8 bits (0-7); I/O DATA2, the least<br>significant bits (8-15). |

| I/O INPUT                          | 28           | OUT        | Indicates direction of I/O transfer. When low, indicates a transfer from the mN601; when<br>high, a transfer to the mN601.                                                                                                                                                                   |

| I/O CLOCK                          | 27           | 1/0        | Synchronizes all I/O transfers to and from the mN601. Holding I/O CLOCK low for $10\mu$ secs resets the microcomputer. I/O CLOCK should not be pulled low when I/O INPUT is in the low state.                                                                                                |

| EXTINT                             | 6            | IN .       | Active low. When asserted low by a device, initiates a program interrupt, providing CPU interrupts are enabled.                                                                                                                                                                              |

|                                    |              |            | When the mN601 is in the HALT state (see below), it is started by generating a program interrupt.                                                                                                                                                                                            |

| DCHINT                             | 5            | IN         | Active low. When asserted low by a device, the CPU will execute a data channel break.                                                                                                                                                                                                        |

|                                    |              |            | The mN601 responds to data channel break requests while it is in the HALT state as<br>well as during operations.<br><b>CPU CONTROL</b>                                                                                                                                                       |

| HALT                               | 37           | Ουτ        | Active high. When the CPU is halted (idling), as the result of either resetting the CPU by<br>pulling I/O CLOCK low or the execution of a HALT instruction, HALT generates a<br>sequence of .417MHz pulses.                                                                                  |

|                                    |              |            | In the HALT state, the mN601 performs the following functions:<br>It generates Request Enable signals (see mN601 I/O Operations section) that<br>synchronize program interrupt and data channel requests.                                                                                    |

|                                    |              |            | <ul> <li>It responds to program interrupts and data channel requests. (The normal way to start<br/>the mN601 is to generate a program interrupt.)</li> </ul>                                                                                                                                 |

|                                    |              |            | <ul> <li>It generates dynamic RAM refresh signals to prevent the loss of information stored in<br/>RAM.</li> </ul>                                                                                                                                                                           |

| CLAMP                              | 35           | IN         | Active low. When the mN601 is first powered up, $\overline{\text{CLAMP}}$ should be held low for a minimum of 100 $\mu$ sec. Then, when it goes high, the CPU is properly initialized and enters the HALT state.                                                                             |

| PAUSE                              | 33           | Ουτ        | Active low. PAUSE goes to the low level for a period of 240ns when the CPU is not using memory. During this period it is permissible to disable the $\phi$ 1 and $\phi$ 2 clocks, thus allowing multiporting of memory.                                                                      |

|                                    |              |            | POWER                                                                                                                                                                                                                                                                                        |

| V <sub>BB</sub>                    | 1<br>17      |            | -4.25V <u>+</u> .5V                                                                                                                                                                                                                                                                          |

| V <sub>CC</sub><br>V <sub>DD</sub> | 38           |            | +5V <u>+</u> .25V<br>+10V <u>+</u> 1V                                                                                                                                                                                                                                                        |

| VGG<br>Vss                         | 7<br>8,26,40 |            | +14V <u>+</u> 1V<br>Ground                                                                                                                                                                                                                                                                   |

|                                    | 34           |            | Reserved for future use                                                                                                                                                                                                                                                                      |

|                                    | 36<br>39     |            | Reserved for future use<br>Reserved for future use                                                                                                                                                                                                                                           |

|                                    |              | l          |                                                                                                                                                                                                                                                                                              |

3

## ARCHITECTURE

The mN601 is a 16-bit parallel word central processing unit which executes the full NOVA line minicomputer instruction set, including an extended instruction set for stack and trap routines.

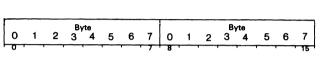

The instruction set addresses 32,768 words (65,536 bytes) of memory. Each memory address is 15-bits long. Each word is 16-bits long, consisting of two 8-bit bytes. Both words and bytes can be used as operands.

Word

|   | 1.100 |

|---|-------|

|   |       |

| - |       |

|   |       |

|    |    |   |   |    |     |   |   | **0 | "u |   |        |      |     |    |

|----|----|---|---|----|-----|---|---|-----|----|---|--------|------|-----|----|

|    |    |   |   | By | /te |   |   |     |    |   | Byte   |      |     |    |

|    | 0  | 1 | 2 | 3  | 4   | 5 | 6 | 7   | 0  | 1 | 21314  | 1516 | 317 |    |

|    | 0  | 1 | 2 | 3  | 4   | 5 | 6 | 7   | 8  | 9 | 10111: | 2131 | 415 |    |

| MS | SВ |   |   |    |     |   |   |     |    |   |        |      | L   | SB |

One word containing two bytes

The mN601 communicates with memory via a bi-directional, 16-bit parallel address and data bus. Three control lines direct the four memory operations: read, write, read-modify-write and refresh.

The mN601 communicates with I/O controller interfaces via two, bi-directional, serial lines that carry data and I/O commands. One control line indicates the direction of transfer, to or from the CPU, and a clock line synchronizes the transfer of information. Two interrupt lines, programmed I/O and data channel, allow I/O interfaces to request processor time.

The Expanded Block Diagram shows the internal architecture of the mN601, together with the memory bus, the I/O bus, and their respective control lines.

Data Genera

Data General Corporation, Westboro, Massachusetts 01581

### EXPANDED BLOCK DIAGRAM

Within the mN601, information is stored in the thirteen registers listed below.

|                                                                                                                                                                                                                                                                                                                                   | CFU INTERNAL REGISTERS                                                        |                                                                                                                                             |  |  |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| REGISTERS                                                                                                                                                                                                                                                                                                                         | USER<br>ACCESSIBLE                                                            | SIZE                                                                                                                                        |  |  |  |  |  |  |  |  |

| accumulator 0<br>accumulator 1<br>accumulator 1<br>accumulator 2<br>accumulator 3<br>program counter<br>stack pointer<br>frame pointer<br>carry bit<br>interrupt enable bit (ION)<br>real-time-clock enable bit (RTC ON)<br>real-time-clock request bit (RTC RQ)<br>stack overflow request bit (SO RQ)<br>refresh address counter | yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>yes<br>no<br>no<br>no | 16 bits<br>16 bits<br>16 bits<br>16 bits<br>15 bits<br>15 bits<br>15 bits<br>15 bits<br>1 bit<br>1 bit<br>1 bit<br>1 bit<br>1 bit<br>6 bits |  |  |  |  |  |  |  |  |

### CPU INTERNAL REGISTERS

- The four accumulators provide scratchpad memory, or work space, during program execution.

- The program counter contains a 15-bit memory address that is used by the processor when fetching the next instruction from memory during program execution. When the instruction is completed, the program counter is either automatically incremented by one or is modified by the program, before the next instruction is fetched.

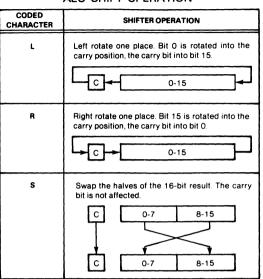

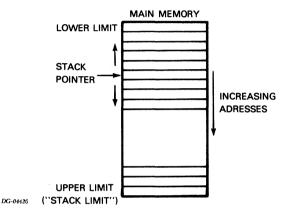

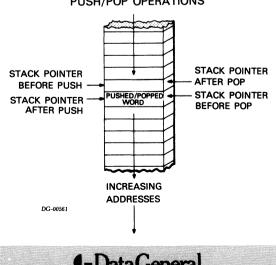

- The stack pointer contains the memory address of the highest location in memory used by the stack. As information is pushed onto the stack, this address is appropriately incremented; as information is popped off the stack, the address is decremented.

- The frame pointer contains the memory address of a location within the stack. When a RETURN instruction is executed, this address is used as a reference for retrieving information from the stack.

- The carry bit reflects the results of certain arithmetic computations performed by the arithmetic logic unit (ALU), e.g., addition overflow.

- The interrupt enable bit can be controlled by the program. When enabled (set to 1), the processor responds to program interrupt requests.

- The real-time-clock enable bit is set by the program. When enabled (set to 1), the real-time clock contained in the processor generates an interrupt at 1.8432ms intervals.

- The real-time-clock request bit generates a program interrupt at fixed intervals of 1.8432ms when both the real- time clock and interrupts are enabled.

- The stack overflow request bit generates a program interrupt when the stack overflows a 256-word memory address boundary, e.g., 377<sub>8</sub> to 400<sub>8</sub>.

- The refresh address counter generates a 6-bit address specifying 64 numbers used to address 1/64 of all the available memory to be refreshed. All 32,768 RAM memory locations are refreshed at least once every 1.8432ms.

2

# mN601 INSTRUCTION SET

1000

## INTRODUCTION TO INSTRUCTION SET

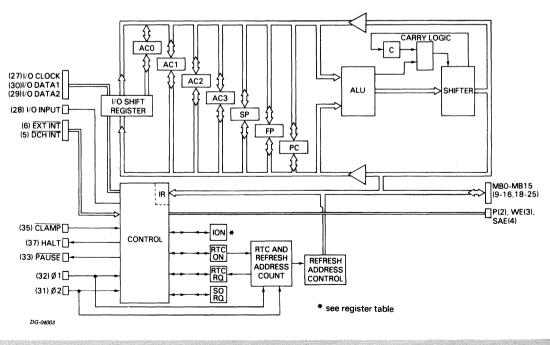

Each mN601 (microNOVA) instruction is contained in one 16-bit word. Programs for the mN601 consist of sequences of instructions which are stored in external memory. The order in which these instructions are executed depends on the 15-bit memory address in the program counter register. During program execution, the processor sends this address to memory and fetches the contents of the specified memory location, via its memory address/data pins. During the execution of an instruction, information is moved between the processor's internal registers, memory or I/O data pins. When the instruction is completed, the program counter is updated. The CPU uses the contents of the program counter to address the next location.

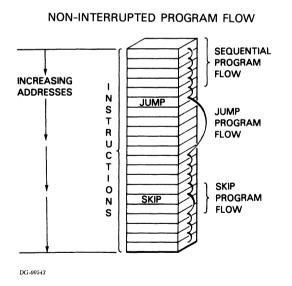

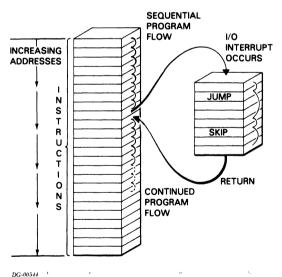

Sequential operation can be altered by a jump or conditional skip instruction or by an interrupt. Jump instructions load a new access in the program counter; conditional skip instructions increment the program counter address by two if a specified test is true. In both cases, sequential operation is resumed from the updated address in the program counter. When the program is interrupted (e.g., I/O external interrupts, real-time clock interrupts, fault conditions of various kinds), the interrupt facility stores the next sequential program address in a specified location in memory so that the interrupt handler can return control to the interrupted program at the proper entry point. Then, the program counter is loaded with the memory address of the interrupt handler program and sequential operation resumes.

### **PROGRAM FLOW**

The microNOVA (mN601) instruction set can be divided into five groups of operations:

- Memory reference

- Fixed point arithmetic and logical operations

- Stack manipulation

- I/O functions

- CPU I/O functions

Each instruction is formatted in a 16-bit (one word) field. In the instruction descriptions that follow, the mnemonics are those recognized by Data General's Assembler. See the microNOVA Programmer's Reference (DGC No. 015-000050) for detailed programming information, including the use of instruction set options, such as conditional skips and flag commands.

**NOTE:** When the instructions described below are executed, the mN601 pins follow the protocol specified by the instructions. It is assumed that the mN601 is interfaced with mN603 I/O controllers and some amount of memory.

## MEMORY REFERENCE INSTRUCTIONS

This instruction group moves data between accumulators and memory, modifies the contents of memory, and alters the program flow.

Locations in memory are sequentially numbered from 00000 through 777778, so that each memory address is 15 bits long.

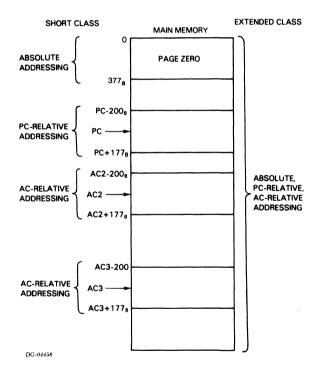

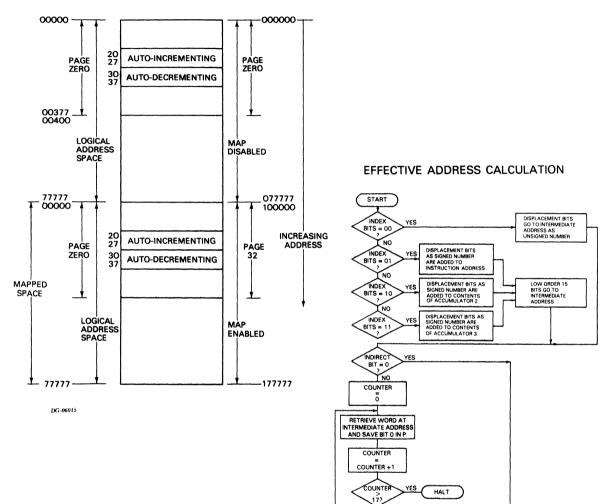

#### ADDRESSING MODES

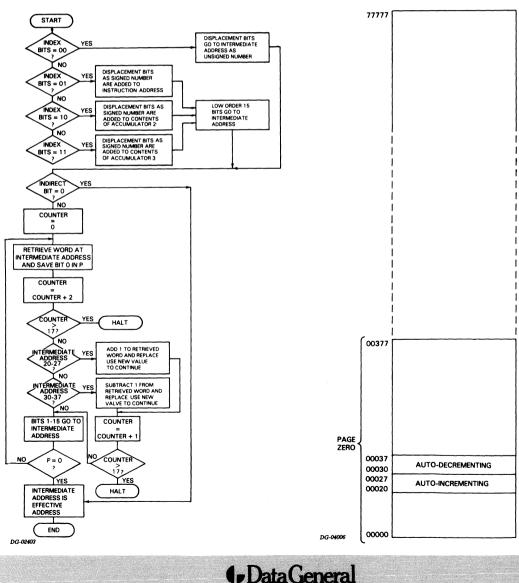

Memory reference instructions provide a variety of addressing modes for accessing 32,768 memory loctions: absolute, PC relative, and indexed (via accumulator 2 or 3). In addition, the processor supports eight levels of conventional indirect (deferred) addressing and five levels of indirect addressing through auto-incrementing/decrementing locations.

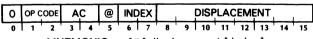

When instructions that reference memory are executed, the processor calculates an effective 15-bit address using bits 5 through 15 of the memory reference instruction field shown below.

### MEMORY REFERENCE INSTRUCTION FORMAT

|   |   |   |   |   | @ | IND | EX |   | 1 | DIS | PLA | CEMI | ENT |    |    |

|---|---|---|---|---|---|-----|----|---|---|-----|-----|------|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6   | 7  | 8 | 9 | 10  | 11  | 12   | 13  | 14 | 15 |

Bit 5 = Indirect bit; Bits 6 and 7 = Address mode: 00 = Absolute

01 = PC relative 10 = AC2 indexed

11 = AC3 indexed

In all but the absolute mode, the displacement is a signed number within the range -128 through +127. Signed numbers utilize the two's complement representation for negatives.

### EFFECTIVE ADDRESS CALCULATION

| Absolute    | Displacement is an unsigned number within the range 00000-00377 <sub>8</sub> that addresses one of the first 256 locations in memory, referred to as Page Zero. If the indirect bit is 0, the displacement is the effective address; if it is 1, the displacement is an indirect address (see the description of indirect addressing below). |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC relative | Displacement is a signed number that is added to the contents of the program counter. If the indirect bit is 0,the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                                       |

| AC2 indexed | Displacement is a signed number that is added to the contents of accumulator 2. If the indirect bit is 0, the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                                            |

| AC3 indexed | Displacement is a signed number that is added to the contents of accumulator 3. If the indirect bit is 0, the results of the addition are the effective address; if it is 1, the results are an indirect address.                                                                                                                            |

NOTE: A memory address is always 15 bits long. When the results of an addition overflow 15 bits, the overflow is ignored.

Example: Program Counter =  $77774_8$ Displacement =  $+012_8$

Result = 000006 8; not 100006 8

### Indirect Addressing

When the indirect bit (bit 5) contains a 1, the calculated address is an intermediate (indirect) address that points to an effective address stored in memory. In this case, the processor fetches the contents of the calculated address and tests bit 0 (indirect sign bit when stored in memory). If it is 0, bits 1 through 15 of the contents of the indirect address are used as the effective address; if it is 1, bits 1 through 15 are used as an indirect address. In the latter case, the indirection chain continues until the processor either fetches a word in which bit 0 equals 0 (in this case, the processor has the effective address) or has executed eight levels of indirection (or five levels if the indirection chain accesses auto-incrementing/decrementing locations, explained below).

An internal counter is used to control the number of indirect addresses through which the processor searches for an effective address. This counter is initialized when the indirect bit is set to 1. Each time a word in the indirection chain is retrieved from memory the counter is incremented by two (or by three if an auto-increment or decrement location is indirectly addressed). If the counter becomes greater than 17 before an effective address is retrieved, the processor halts.

#### Auto-Incrementing/Decrementing

Memory locations with addresses within the range 020 8 through 0278 are called auto-incrementing locations. When one of these locations is indirectly addressed, the processor automatically increments bits 0 through 15 of the contents of the indirect address before using these bits as either an effective or indirect address. The updated contents are written back into the auto-incrementing location.

Memory locations with addresses within the range 030 <sup>B</sup> through 037 <sup>B</sup> are called auto-decrementing locations. When one of these locations is indirectly addressed, the processor automatically decrements bits 0 through 15 of the contents of the indirect address before using these bits as either an effective or indirect address. The updated contents are written back into the auto-decrementing location.

**NOTE 1:** When referencing auto-increment/decrement locations, the state of bit 0 before the increment or decrement is the condition upon which the continuation of the indirection chain is based. For example: if an auto-increment location contains 177778 and the location is referenced as part of an indirection chain, location 0 will be the next indirect address in the chain; not the effective address.

NOTE 2: When a non-existing memory address is specified in a memory reference instruction, the contents will appear as all ones.

### MEMORY ADDRESSING

| MODE        | INDEX<br>BITS | MEMORY ADDRESSING<br>CAPABILITY (OCTAL) |

|-------------|---------------|-----------------------------------------|

| Absolute    | 00            | 00000-00377                             |

| PC Relative | 01            | 00000-77777                             |

| AC2 Indexed | 10            | 00000-77777                             |

| AC3 Indexed | 11            | 00000-77777                             |

MEMORY

## ADDRESS CALCULATION

Data General Corporation, Westboro, Massachusetts 01581

### NO ACCUMULATOR-EFFECTIVE ADDRESS INSTRUCTIONS

The general format for this class of instruction is shown below. The table shows the specific format and function for each instruction.

| 0 | 0 | 0 | OP C | ODE | @ | INC | INDEX |   | DISPLACEMENT |    |    |    |    |    |    |

|---|---|---|------|-----|---|-----|-------|---|--------------|----|----|----|----|----|----|

| 0 | 1 | 2 | 3    | 4   | 5 | 6   | 7     | 8 | 9            | 10 | 11 | 12 | 13 | 14 | 15 |

INSTRUCTION FORMATS AND FUNCTIONS

| MNEMONIC | MEANING                          | FUNCTION *                                                                                                                                                                         | INSTRUCTION FORMAT                                                      |

|----------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| JMP      | Jump                             | Compute (E) and load E into PC.                                                                                                                                                    | 0 0 0 0 0 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

| JSR      | Jump To<br>Subroutine            | Compute E. Store contents<br>of PC+1 in bits 1-15 of AC3<br>and set bit 0 to 0; then, load<br>E into PC.                                                                           | 0 0 0 0 1 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

| ISZ      | Increment<br>And Skip<br>If Zero | Compute E. Increment<br>contents of location E and<br>write results back into<br>location E. If results equal<br>000000, increment PC by<br>two; otherwise increment<br>PC by one. | 0 0 0 1 0 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

| DSZ      | Decrement<br>And Skip<br>If Zero | Compute E. Decrement<br>contents of location E and<br>write results back into<br>location E. If results equal<br>000000, increment PC by<br>two; otherwise increment<br>PC by one. | 0 0 0 1 1 @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 |

\*E = effective address; AC = accumulator

### **ONE ACCUMULATOR-EFFECTIVE ADDRESS INSTRUCTIONS**

The general format and accumulator code for this class of instruction are shown below. The table shows the specific format and function for each instruction.

|   |      |     | _   |     |   |         |   | _ | _        | -   |    |    |    |    |    |

|---|------|-----|-----|-----|---|---------|---|---|----------|-----|----|----|----|----|----|

| 0 | OP C | ODE | Α   | ç   | @ | @ INDEX |   | 1 | 1        | ENT |    |    |    |    |    |

| 0 | 1    | 2   | 3   | 4   | 5 | 6       | 7 | 8 | 9        | 10  | 11 | 12 | 13 | 14 | 15 |

|   |      |     | ſ   | AC  |   |         |   |   | <br>>    |     |    | ٦  |    |    |    |

|   |      |     | - L | AC  | _ | Bits    |   |   | <u> </u> |     |    |    |    |    |    |

|   |      |     | - [ | ACO | ) | 0       |   |   |          | 0   | 7  |    |    |    |    |

|   |      |     |     | AC1 |   | ł       |   |   | 0 1      |     | 1  |    |    |    |    |

|   |      |     |     | AC2 |   | 1       |   |   | 1        |     | 0  |    |    |    |    |

|   |      |     |     | AC  | 3 |         |   |   | 1        |     | 1  |    |    |    |    |

#### INSTRUCTION FORMATS AND FUNCTIONS

| MNEMONIC | MEANING              | FUNCTION *                                                      | INSTRUCTION FORMAT                                                                                                                                                                                                                                    |  |  |  |  |

|----------|----------------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| LDA      | Load<br>Accumulator  | Compute E. Load specified<br>AC with contents of location<br>E. | 0 0 1 AC @ INDEX DISPLACEMENT<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                                                                                                                                                                                |  |  |  |  |

| STA      | Store<br>Accumulator | Compute E. Store contents<br>of specified AC in location<br>E.  | 0         1         0         AC         @         INDEX         DISPLACEMENT           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |  |  |  |  |

\* E = effective address; AC = accumulator

# mN601 TRAP INSTRUCTION

## TRAP INSTRUCTION

This instruction can be used as a single word call to subroutines containing extended instructions not implemented by the mN601. The format of the TRAP instruction is shown below.

| MNEMONIC | MEANING | FUNCTION                                                                                                                                                                                  | INSTRUCTION FORMAT                                                                                                                                                                                                                    |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRAP     | Тгар    | The address of this instruction is placed in memory location $46_8$ and bit 0 of that location is set to 0. Then, the processor performs a jump indirect through memory location $47_8$ . | 1         TRAP NUMBER         1         0         0         0           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |

### INSTRUCTION FORMAT AND FUNCTION

## **ARITHMETIC/LOGICAL INSTRUCTIONS**

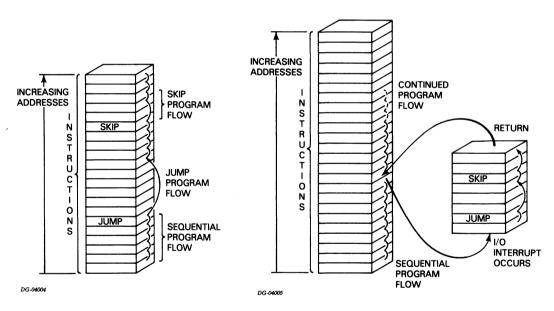

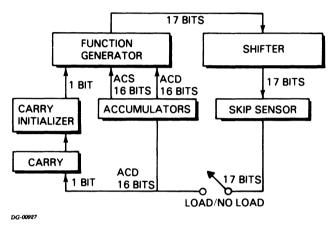

This instruction group performs arithmetic and logical operations on the contents of one or two accumulators. In some cases, it changes the value of the carry bit and, if specified, manipulates and/or tests the results of the operations.

The logical organization of the mN601's internal arithmetic logic unit (ALU) is shown below.

DG-00927

### TWO ACCUMULATOR-MULTIPLE OPERATION

| 1 | 1 ACS AC |   | D | OP CODE |   |   |   |   |   |    |    |    |    |    |    |

|---|----------|---|---|---------|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1        | 2 | 3 | 4       | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

|                                              | ACS ACD<br>Bits 1 2 3 4    |

|----------------------------------------------|----------------------------|

| AC = accumulator<br>ACS = source accumulator | AC0 0 0 0 0                |

| ACD = destination accumulator                | AC1 0 1 0 1<br>AC2 1 0 1 0 |

|                                              | AC3 1 1 1 1                |

Each instruction specifies two accumulators, source and destination, that supply the function generator with operands. The function generator performs the operation specified by the operation code, e.g., add, subtract, and produces a carry bit whose value depends on three quantities: an initial value specified by the instruction, the inputs, and the function performed. The initial value can be derived either from the previous value of the carry bit or a new value specified by the instruction.

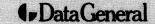

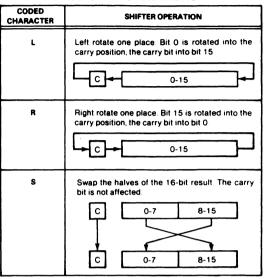

The 17-bit (16 bits plus the carry bit) result of the function generator goes to the shifter. Depending upon the shift operation specified, the results are either passed undisturbed through the shifter or they are manipulated in one of the following ways: the 17-bit result is rotated one bit position, either left or right; or, the two 8-bit halves are swapped without affecting the carry bit.

# **mN601 ARITHMETIC/LOGICAL INSTRUCTIONS**

#### ALU SHIFT OPERATION

DG-04423

The 17-bit output of the shifter can be tested for a conditional skip. The skip sensor tests either, or both, the carry bit or the 16-bit result of the shifter, depending upon the instruction, to determine if either, or both, is equal or not equal to zero.

After the skip sensor has tested the output of the shifter, the 17- bit result of the shifter is either loaded or not loaded, depending upon the instruction, into the destination accumulator and the carry bit.

#### ALU CARRY, SHIFT, LOAD OPTIONS

| CLASS<br>ABBREV. | CODED<br>CHARACTER | RESULT<br>BITS | OPERATION                                                                                                                                  |

|------------------|--------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| с                | (option omitted)   | 00             | Do not initialize the carry bit                                                                                                            |

|                  | z                  | 01             | Initialize the carry bit to 0.                                                                                                             |

|                  | 0                  | 10             | Initialize the carry bit to 1                                                                                                              |

|                  | с                  | 11             | Initialize the carry bit to the complement of its present value.                                                                           |

| ян               | (option omitted)   | 00             | Leave the result of the arithmetic or logical operation unaffected.                                                                        |

|                  | L                  | 01             | Combine the carry and the 16-bit result into a 17-bit number and rotate it one bit left.                                                   |

|                  | R                  | 10             | Combine the carry and the 16-bit result into a 17-bit number and rotate it one bit right                                                   |

|                  | s                  | 11             | Exchange the two 8-bit halves of the 16-bit result without affecting the carry.                                                            |

| #                | (option omitted)   | 0              | Load the result of the shift operation into ACD.                                                                                           |

|                  | #                  | 1              | Do not load the result of the shift operation into ACD.                                                                                    |

| #<br>DG-04424    | (option omitted)   | 0              | result without affecting the carry.<br>Load the result of the shift operation into ACI<br>Do not load the result of the shift operation in |

#### ALU SKIP OPTIONS

| CLASS<br>ABBREV. | CODED<br>CHARACTER | RESULT<br>BITS | OPERATION                              |

|------------------|--------------------|----------------|----------------------------------------|

| SKIP             | (option omitted)   | 000            | Never skip                             |

|                  | SKP                | 001            | Always skip                            |

|                  | SZC                | 010            | Skip if carry = 0                      |

|                  | SNC                | 011            | Skip if carry ≠ 0                      |

|                  | SZR                | 100            | Skip if result = 0                     |

|                  | SNR                | 101            | Skip if result ≠ 0                     |

|                  | SEZ                | 110            | Skip if either carry or result = 0     |

|                  | SBN                | 111            | Skip if both carry and result $\neq$ 0 |

NOTE: Instructions in the Two Accumulator-Multiple Operation format must NOT have both the 'No Load' and the 'Never Skip' options specified at the same time. These bit combinations are used by other instructions in the instruction set.

# mN601 ARITHMETIC/LOGICAL INSTRUCTIONS

### **TWO ACCUMULATOR-MULTIPLE OPERATION INSTRUCTIONS**

In the function descriptions below, it is assumed that the carry bit is set to the specified value and the shift, conditional skip and load functions are performed as stipulated in the instruction field. When a conditional skip is specified in the instruction, the program counter is incremented an additional time if the condition is true.

| MNEMONIC | MEANING           | FUNCTION                                                                                                                                                                                                                          | INSTRUCTION FORMAT                                                                                                                                                                                                                                                          |

|----------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СОМ      | Complement        | The one's complement of<br>the contents of ACS is<br>placed in the shifter. The<br>output of the shifter is<br>placed in ACD and the carry<br>bit.                                                                                | 1         ACS         ACD         0         0         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15           |

| NEG      | Negate            | The two's complement of<br>the contents of ACS is<br>placed in the shifter. If the<br>operation produces a carry<br>of 1, carry is complemented.<br>The output of the shifter is<br>placed in ACD and the carry<br>bit.           | 1         ACS         ACD         0         1         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15           |

| MOV      | Move              | Contents of ACS are placed<br>in the shifter. The output of<br>the shifter is placed in ACD<br>and the carry bit.                                                                                                                 | 1         ACS         ACD         0         1         0         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |

| INC      | Increment         | Contents of ACS are<br>incremented by one. If the<br>operation produces a carry<br>of 1, carry is complemented.<br>The output of the shifter is<br>placed in ACD and the carry<br>bit.                                            | 1         ACS         ACD         0         1         1         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |

| ADC      | Add<br>Complement | The one's complement of<br>the contents of ACS is<br>added to the contents of<br>ACD. If the operation<br>produces a carry of 1, carry<br>is complemented. The<br>output of the shifter is<br>placed in ACD and the carry<br>bit. | 1 ACS ACD 1 0 0 SH C # SKIP<br>0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15                                                                                                                                                                                                        |

### INSTRUCTION FORMATS AND FUNCTIONS

2

# mN601 ARITHMETIC/LOGICAL INSTRUCTIONS

| MNEMONIC | MEANING  | FUNCTION                                                                                                                                                                                                                          | INSTRUCTION FORMAT                                                                                                                                                                                                                                                          |

|----------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SUB      | Subtract | The two's complement of<br>the contents of ACS is<br>added to the contents of<br>ACD. If the operation<br>produces a carry of 1, carry<br>is complemented. The<br>output of the shifter is<br>placed in ACD and the carry<br>bit. | 1         ACS         ACD         1         0         1         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |

| ADD      | Add      | The contents of ACS are<br>added to the contents of<br>ACD. If the operation<br>produces a carry of 1, the<br>carry is complemented. The<br>output of the shifter is<br>placed in ACD and the carry<br>bit.                       | 1         ACS         ACD         1         1         0         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15 |

| AND      | And      | The contents of ACS and<br>ACD are logically AND'd.<br>The output of the shifter is<br>placed in ACD and the carry<br>bit.                                                                                                        | 1         ACS         ACD         1         1         SH         C         #         SKIP           0         1         2         3         4         5         6         7         8         9         10         11         12         13         14         15           |

### INSTRUCTION FORMATS AND FUNCTIONS (CONT)

### MULTIPLY/DIVIDE INSTRUCTIONS

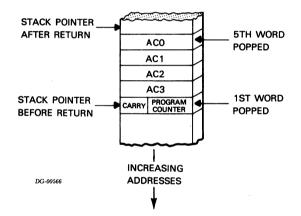

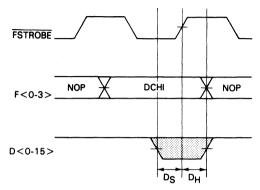

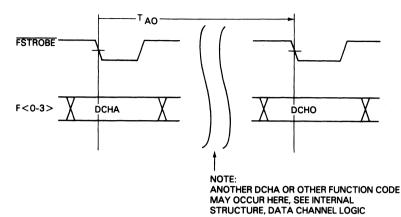

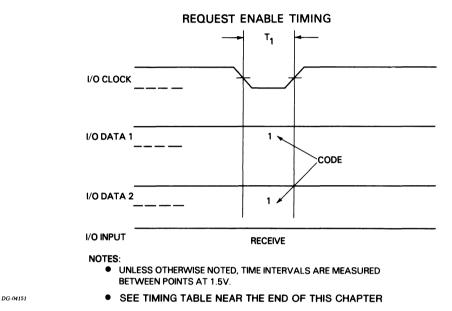

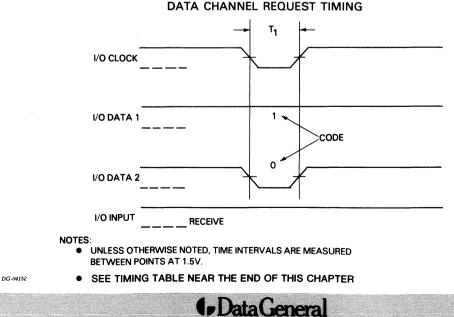

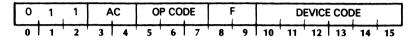

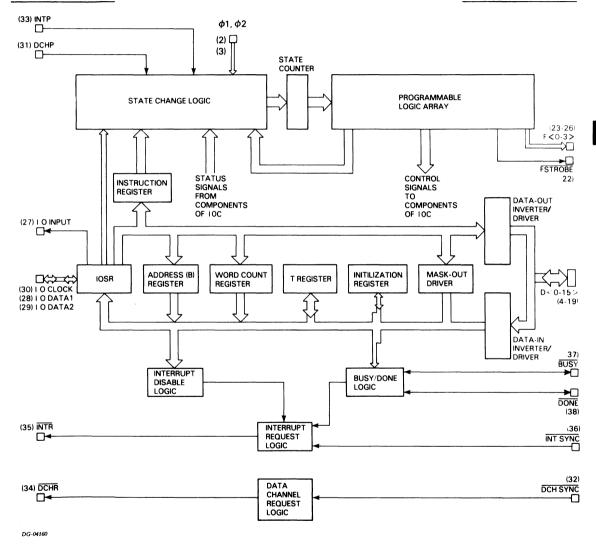

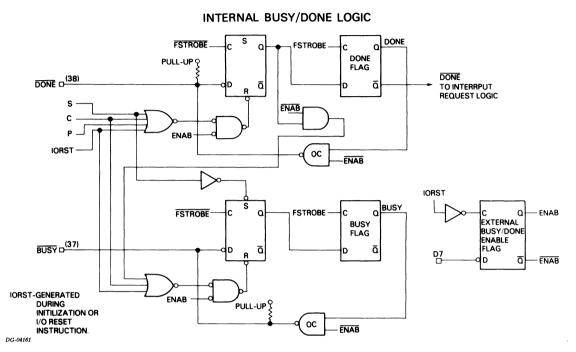

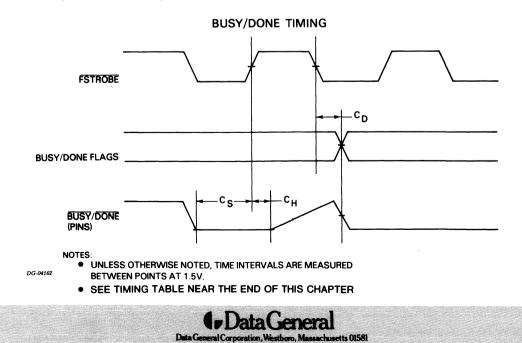

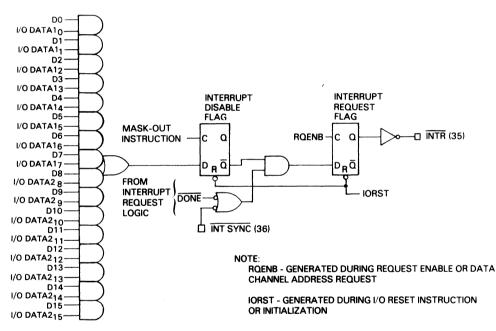

The following instructions utilize an I/O instruction format and bits 10 to 15 specify device code 1. For this reason, device code 1 is an illegal device code and should not be assigned to any I/O interface device.