# NOVA® 4 PROGRAMMER'S REFERENCE MANUAL

~

# NOTICE

Data General Corporation (DGC) has prepared this manual for use by DGC personnel, licensees, and customers. The information contained herein is the property of DGC and shall not be reproduced in whole or in part without DGC's prior written approval.

Users are cautioned that DGC reserves the right to make changes without notice in the specifications and materials contained herein and shall not be responsible for any damages (including consequential) caused by reliance on the materials presented, including, but not limited to typographical, arithmetic, or listing errors.

NOVA, INFOS, and ECLIPSE are registered trademarks of Data General Corporation, Westboro, Massachusetts. DASHER and microNOVA are trademarks of Data General Corporation, Westboro, Massachusetts.

## **FIRST EDITION**

(First Printing November 1978)

Ordering No. 014-000617 ©Data General Corporation, 1978 All Rights Reserved Printed in the United States of America Rev. 00, November 1978

# CONTENTS

| <b>CHAPTER I</b> | <b>NOVA 4 SYSTEM</b> |

|------------------|----------------------|

|------------------|----------------------|

1 INTRODUCTION

# CHAPTER II INTERNAL STRUCTURE

- 1 INTRODUCTION

- **1** INFORMATION FORMATS

- 4 INFORMATION ADDRESSING

- 6 **PROGRAM EXECUTION**

# CHAPTER III INSTRUCTIONS SETS

- 1 INTRODUCTION

- **1** INSTRUCTION FORMATS

- 4 CODING AIDS

- 4 FIXED POINT ARITHMETIC

- 7 LOGICAL OPERATIONS

- 8 STACK MANIPULATION

- 9 STACK MANIPULATION INSTRUCTIONS

- 11 **PROGRAM FLOW ALTERATION**

- **13 BYTE INSTRUCTIONS**

# CHAPTER IV INPUT/OUTPUT

- 1 INTRODUCTION

- **1** OPERATION OF I/O DEVICES

- 2 PRIORITY INTERRUPTS

- 2 DATA CHANNEL

- 3 CODING AIDS

- 5 CENTRAL PROCESSOR FUNCTIONS

- 8 POWER FAIL

- 9 REAL-TIME CLOCK

# CHAPTER V PROCESSOR OPTIONS

- 1 INTRODUCTION

- 1 MULTIPLY/DIVIDE

- **3 MEMORY MANAGEMENT**

- 5 MEMORY ALLOCATION AND PROTECTION

- **10** SUPERVISOR PROGRAMMING FOR THE NOVA 4

- 12 FLOATING POINT UNIT

- **13** INSTRUCTION SET

CHAPTER VI VIRTUAL CONSOLE (VC)

APPENDIX A I/O DEVICE CODES AND DATA GENERAL MNEMONICS

- APPENDIX B OCTAL AND HEXADECIMAL CONVERSION

- APPENDIX C ASCII CHARACTER CODES

# Chapter I NOVA 4 SYSTEM

# INTRODUCTION

The NOVA 4 is a general purpose, four-accumulator, stored-program computer, with a word length of 16 bits. The maximum amount of main memory is 64 Kbytes without a MAP and 256 Kbytes or 131,072 16-bit words with a MAP.

Memory can be addressed either directly or by using indirect addresses. A data channel is provided to enable rapid data transfer between main memory and peripheral devices.

The standard instruction set contains instructions that perform fixed point arithmetic and logical operations between accumulators, transfer of operands between accumulators and main memory, transfer of program control, and input/output(I/O) operations. Options are available that add instructions to this set. These additional instructions perform such operations as multiply/divide, floating point calculations, and memory allocation and protection.

## **Efficient Basic Instruction Set**

The basic instruction set for the NOVA 4 contains instructions that perform fixed point arithmetic and logical operations between accumulators, transfer of operands between accumulators and main memory, transfer of program control, and I/O operations. All instructions are one 16-bit word in length. The arithmetic and logical instructions have the capability to perform, in one instruction, the following sequence: perform an operation, shift the result one bit left or right, test the result of the shift, and then conditionally skip the next instruction depending upon the outcome of the test. In addition, it is possible to perform this entire sequence without affecting either of the operands. this means that complicated numerical manipulation and testing can be performed using a small number of instructions.

# Stack

A Last-In/First-Out (*LIFO*) or push-down stack is maintained by the NOVA 4 processor. This feature provides a convenient method for saving return information and passing arguments between subroutines. The stack also provides an expandable area for the temporary storage of variables and intermediate results.

# **Floating Point**

The floating point feature allows the manipulation of both single precision (32 bits) and double precision (64 bits) floating point numbers. Single precision gives 6-7 significant decimal digits while double precision gives 15-17 significant decimal digits. The decimal range of a floating point number is approximately  $5.4 \times 10^{-79}$  to  $7.2 \times 10^{+75}$  in either precision.

The floating point feature contains two 64-bit floating point accumulators. Floating point calculations can take place between these two accumulators or between one of the accumulators and operands in main memory.

# **Memory Allocation and Protection**

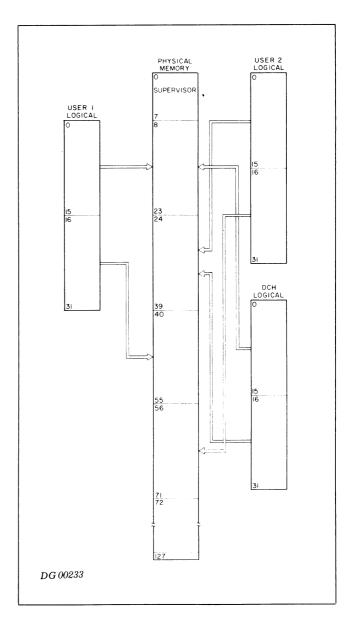

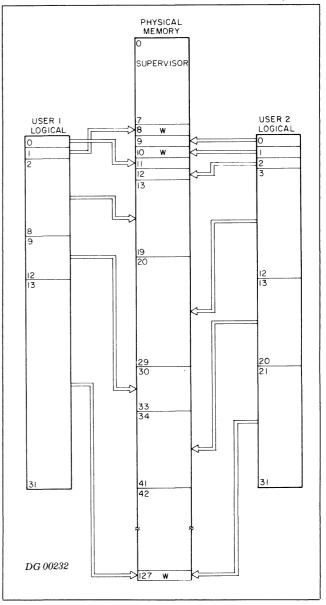

The optional Memory Allocation and Protection unit (MAP) translates logical addresses within the user space to physical memory addresses. The MAP feature holds two user maps and two data channel maps at a time. Only one user map can be enabled at any one time, but both data channel maps are enabled at the same time.

In addition to translating addresses, the feature also performs various protection functions. A user is allowed to access only those blocks of memory allocated to him. This ensures that a user does not reach out of his own areas of memory for either instructions or data. Blocks of memory allocated to a user may be write-protected so that the user may not modify them. This allows blocks of memory containing constants or nonself-modifying procedures to be shared between users.

The MAP detects and inhibits indirection chains that go deeper than 16 levels. This protects the system from becoming disabled by an indirection loop. The MAP also provides I/O protection which allows all I/O devices to be declared accessible or inaccessible to a user.

## Memory

Memory for the NOVA 4 is available in 32 Kbyte, 64 Kbyte, 128 Kbyte and 256 Kbyte modules. All memory is semiconductor.

## **Auto-Increment/Decrement**

If the intermediate address of a short class instruction is in the range  $20-27_8$ , and the indirect bit is 1, the contents of the addressed location are incremented by one. The incremented value is used to continue the addressing chain.

If the intermediate address of a short class in truction is in the range  $30-37_8$ , and the indirect bit is 1, the contents of the addressed location are decremented by one. The decremented value is used to continue the addressing chain.

NOTE: The state of bit 0 before the increment or decrement determines whether the indirection chain is continued. For example: Assume an auto-increment location contains  $177777_8$  (all bits = 1 including bit 0), and the location is referenced as part of an indirection chain. After incrementing, the location contains all zeros. However, bit 0 was 1 before the increment, so 0 will be the next address in the chain rather than the effective address.

### **Power Fail/Auto Restart**

The power fail/auto restart feature of the NOVA 4 provides a *fail-soft* capability in the event of unexpected power loss. In the event of power failure, there is a delay of one to two milliseconds before the processor shuts down. The power fail portion of the feature senses the imminent loss of power and interrupts the processor. The interrupt service routine can then use this delay to store the contents of the accumulators, the program restart address, and other information that will be needed to restart the system.

When power is restored, the action taken by the auto-restart portion of the feature depends upon the position of the lock switch on the front panel. If the switch is not in the *lock* position, the processor remains stopped after power is restored. If the switch is in the *lock* position and battery backup is

operational, then after power is restored, the processor executes the instruction contained in the first location of main memory, restarting the interrupted system.

The battery backup option available with the NOVA 4 operates in conjunction with the power fail/auto restart feature to provide security for semiconductor memories in the event of a power failure. If power fails, the battery backup option will supply power to the memories for a period of up to one-and-one-half hours (depending on the number of memory boards) so that they will not lose their data. If further security is desired, a larger external battery can be attached to ensure the integrity of the memories for extended periods of time.

# **Real-Time Clock**

The real-time clock feature of the NOVA 4 generates a sequence of pulses that is independent of the timing of the processor. The clock will interrupt the system at one of four program-selectable frequencies. The frequencies are: ac line frequency, 10Hz, 100Hz, and 1000Hz.

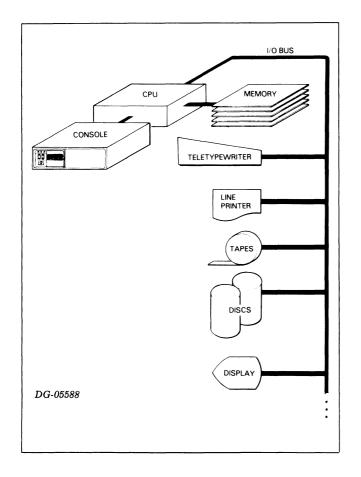

# Input/Output Bus

The input/output (I/O) bus is that portion of the computer that carries commands and data between the central processor and various peripheral devices connected to it. The bus is made up of a six-line device selection network, interrupt circuitry, command circuitry, and sixteen data lines.

### **Device Addressability**

Each I/O device in a NOVA 4 is connected to the six-line device selection network in such a way that each device will only respond to commands that contain its own device code. The fact that the selection network is made up of six lines gives  $2^6 = 64$  unique device codes. Ten of these codes are reserved for specific functions, but there are still 54 device codes available for use with I/O devices.

#### Interrupt Capability

The interrupt circuitry contained in the I/O bus provides the capability for any I/O device to interrupt the system when that device requires service. When a device requests an interrupt, the processor automatically transfers program control to the main interrupt service routine. This routine can either poll all the I/O devices in the system to find out which one initiated the interrupt, or the routine can use a special instruction to identify the source of the interrupt.

The interrupt circuitry of the NOVA 4 also contains the capability to implement up to sixteen levels of priority interrupts. This is done with a 16-bit priority mask. Each level of device priority is associated with

#### **NOVA 4 SYSTEM**

a bit in this mask. In order to suppress interrupts from any priority level, the corresponding bit in the mask is set to 1.

#### Data Channel

Handling data transfers between external devices and memory under program control requires an interrupt plus the execution of several instructions for each word transferred. To allow greater transfer rates, the I/O bus contains circuitry for a data channel through which a device, at its own request, can gain direct access to main memory using a minimum of processor time. At the maximum transfer rate, the data channel effectively stops the processor, but at lower rates, processing continues while data is being transferred.

#### Ease of Interfacing

Due to the straightforward logic and general design of the NOVA 4 I/O bus, customer-provided or customer-designed I/O devices may be easily interfaced to a NOVA 4. Information on how to interface to the NOVA 4 may be found in "The Interface Designer's Reference Manual" (DGC 015-000031).

## **Input/Output Devices**

A comprehensive array of I/O devices is available from Data General for the NOVA 4. This wide choice of devices, ranging from teletypewriters to line printers to video displays for man-machine interaction; and from paper tape to magnetic tape to fixed and moving-head discs for data storage allows a wide spectrum of possible configurations. Also available are various multiplexors and telecommunications adapters, including an IBM 360/370 interface.

### Software

A wide variety of software support is available for the NOVA 4.

Operating systems include the Disc Operating System (DOS), the Real-Time Operating System (RTOS), and the Real-Time Disc Operating system (RDOS).

An assembler is available with all of these operating systems. In addition, many higher-level languages are available. These include Fortran IV and V,  $DG/L^{TM}$ , ALGOL, Extended BASIC, and Business BASIC. Note that not all languages are available in all operating systems.

# Chapter II INTERNAL STRUCTURE

# INTRODUCTION

The basic structure of a NOVA 4 data processing system consists of a central processing unit (CPU), some amount of main memory, the I/O bus, the I/O devices connected to the I/O bus.

Due to the general-purpose design of the NOVA 4, the type, size, and number of memory modules and I/O devices have no effect upon the internal logical structure of the CPU. This chapter deals with the addressing of information and the logical representation of information within the CPU, and is unaffected by those portions of the system outside the CPU.

# **INFORMATION FORMATS**

The basic piece of information within the processor is the binary digit, or *bit*. A bit is capable of representing only two quantities, 0 and 1. However, a bit cannot represent both these values at the same time. At any one point in time, a bit can either represent a 0 or a 1, never both.

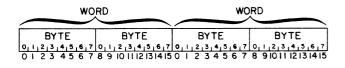

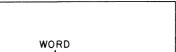

The normal unit of information within the CPU is the word. A word is made up of 16 bits. Because each bit is capable of representing two quantities, a word is capable of representing  $2^{16} = 65,536$  different quantities. A word may be broken into two bytes of 8 bits each. A byte is capable of representing  $2^8 = 256$ different quantities. I/O devices transfer information in units of bits, bytes, words or groups of words called "records" depending upon the device.

# **Bit Numbering**

In order to avoid confusion when talking about the information contained in bytes and words, the bits that make up these units of information are numbered from left to right, with the leftmost (highorder) bit always numbered bit 0. The numbering extends to the right and is always carried out in the decimal number system. The rightmost (low order) bit in a byte is bit 7. The rightmost bit in a word is bit 15.

# **Octal Representation**

Because talking about the binary data contained in bytes and words would quickly become awkward and confusing if each bit were described, the octal representation of binary information will be used in this manual. To convert a piece of binary information to its octal representation, the bits in the quantity are separated into groups of three bits each, starting from the right and proceeding to the left. If the number of bits to be represented is not evenly divisible into groups of three, the leftmost group will contain one or two bits. Each group of bits can now be represented by one of eight different symbols. The digits 0-7. Each encoded digit is called an octal digit. Because each group of bits can contain any one of 8 values, this representation is sometimes called base 8representation.

Another way to represent binary information is the hexadecimal or *hex* representaion. In hexadecimal, the bits in the quantity are separated into groups of four bits each and each group can be represented by one of 16 different symbols. The digits 0-9 are used to represent the quantities 0-9. The letters A-F are used to represent the quantities 10-15. Because each group of bits can contain any one of 16 values, this representation is sometimes called *base 16* representation.

Our normal decimal numbering system is sometimes called *base 10* representation. Because it is sometimes possible to confuse numbers written in hex or octal with those written in decimal, a subscript denoting the base will be used in cases where confusion might occur. Conversion tables for hex to decimal and octal to decimal are contained in Appendix B of this manual.

# **Character Codes**

Within the processor, all information is represented by binary quantities. The CPU does not recognize certain bit combinations as characters and certain other bit combinations as numbers. Sooner or later, however, this information must be transferred outside the computer in some form easily understood by humans. For this reason, some standard correspondence must be made between certain bit combinations and printable symbols. The code used to implement this correspondence in I/O devices available with the NOVA 4 is called the American Standard Code for Information Interchange (ASCII). This code can represent 95 printable symbols plus 33 control functions. A complete table of the codes and their corresponding characters can be found in Appendix C of this manual.

## Information Representation

Even though the CPU does not intrinsically recognize one information type from another, the different instructions in the instruction set expect that the information to be operated on will be in a specific format. In general, there are three different, basic information formats. They are integers, floating point numbers, and logical quantities.

#### Integers

Integers can be represented as either signed or unsigned numbers and carried in either single or multiple precision. Single precision integers are two bytes long, while multiple precision integers are four or more bytes long. Unsigned integers use all the available bits to represent the magnitude of the number. A single two-byte word can represent any unsigned number in the inclusive range 0 to 65,535. Two words taken together as an unsigned, double precision integer can represent any number in the inclusive range 0 to 43,294,967,295.

For signed operations, the two's complement numbering system is used. In this system, the leftmost or high-order bit is used as a sign bit. If the sign bit is 0, the number is positive and the remainder of the bits in the number represent the magnitude of the number as described above. If the sign bit is 1, the number is negative and the remainder of the bits represents the magnitude of the number.

To create the negative of a number in the two's complement scheme, complement all the bits of the number including the sign bit. After the complementing process is finished, add 1 to the rightmost or low-order bit. If the two's complement of a negative number is formed, the result will be the corresponding positive number.

There is only one representation for zero in two's complement arithmetic: it is the number with all bits zero. Forming the two's complement of zero will produce a carry out of the high-order bit and leave the number with all bits zero. Note that 0 is a positive number, i.e., its sign bit is 0.

Because the two's complement scheme has only one representation for 0, there is always one more negative number than there are non-negative numbers. The most negative number is a number with a 1 in the sign bit and all other bits 0. The positive value of this number can not be represented in the same number of bits as used to represent the negative number.

#### INTERNAL STRUCTURE

A single two-byte word can represent any signed number in the inclusive range -32,768 to +32,767. Two words taken together as a signed, double precision integer can represent any number in the inclusive range -2,147,483,648 to +2,147,483,647.

It is a property of numbers using the two's complement scheme that addition and subtraction of signed numbers are identical to addition and subtraction of unsigned numbers. The CPU just treats the sign bit as the most significant magnitude bit.

#### **Floating Point**

The floating point feature of the NOVA 4 allows operations on signed numbers having a much larger range than those normally represented as integers. It would take a 16-word multiple precision integer to represent the range of a NOVA 4 floating point number. Since floating point numbers occupy either two words for single precision or four words for double precision, and the floating point feature is much faster than multiple precision integer software routines, floating point arithmetic is used when numbers having a large range must be manipulated.

A floating point number is made up of three parts: the sign, the exponent, and the mantissa. The value of a floating point number is defined to be:

MANTISSA X 16 RAISED TO THE TRUE VALUE OF THE EXPONENT FIELD

The number is signed according to the value of the sign bit. If the sign bit is 0, the number is positive; if the sign bit is 1, the number is negative.

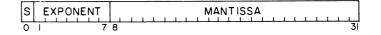

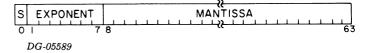

Floating point numbers are represented internally by either 32 bits (single precision) or 64 bits (double precision).

The formats are shown below:

**Single Precision**

#### **Double Precision**

Bit zero is the sign bit: 0 for positive, 1 for negative.

Bits 1-7 contain the exponent. This is the power to which 16 must be raised in order to give the correct value to the number. So that the exponent field may accommodate a large range, *Excess 64* representation is used. This means that the value in the exponent field is 64 greater than the true value of the exponent. If the exponent field is zero, the true value of the exponent is -64. If the exponent field is 64, the true value of the exponent is 0. If the exponent field is 127, the true value of the exponent is 63.

Bits 8-31 for single precision and bits 8-63 for double precision contain the mantissa. This means that bit 8 of the floating point number is bit 0 of the mantissa. The mantissa is always a positive fraction greater than or equal to 1/16 and less than 1. The *binary point* can be thought of as being just to the left of bit 8. Continuing this concept then, bit 8 represents the value 1/2, bit 9 represents the value 1/4, bit 10 represents the value 1/8, and so on.

In order to keep the mantissa in the range of 1/16 to 1, the results of floating point arithmetic are *normalized*. Normalization is the process whereby the mantissa is shifted left one hex digit at a time until the high-order four bits represent a nonzero quantity. For every hex digit shifter, the exponent is decreased by one. Since the mantissa is shifted four bits at a time, it is possible for the high-order three bits of a normalized mantissa to be zero.

Zero is represented by a floating point number with all bits zero. This is true for both single and double precision. This is known as *true zero*. When a calculation results in a zero mantissa, the floating point processor automatically converts the number to a true zero. Note that true zero is positive. It is not possible to obtain negative zero as the result of a calculation.

#### **Logical Quanities**

Logical operations in the NOVA 4 can be performed upon individual bits, bytes, or words. When using the logical operations, quantities operated on are treated as unstructured binary quantities. The number of bits, bytes, or words operated upon depends on the particular instruction.

# INFORMATION ADDRESSING

The information formats described in the preceding section give a way of representing different types of data in main memory. Operations cannot be performed upon these data types, however, unless they can be addressed by the CPU. The address of a piece of information is its location in main memory. Once the CPU knows the address of a piece of information, the desired operation can be performed.

## Word Addressing

Main memory is partitioned into 2-byte words, and each word has an address. The first word in memory has the address 0. The next word has the address 1, the next word has the address 2, and so on. Word addressing is used to address integers, floating point numbers, and logical quantities that are formatted in units of words.

**Data General Corporation**

## **Effective Address Calculation**

There are six instructions in the NOVA 4 instruction set that directly reference memory using word addressing. These instructions use eleven bits in the instruction to define the address of the desired word. The resultant address is called the effective address or E, and the calculation is called the *effective* address calculation.

The eleven bits in an instruction that are used in the effective address calculation, are bits 5-15. Their format is shown below.

| Γ |   |   |   |   |   | @ | IN | DEX |   |   | D  | ISPL | ACE | MEN | r  |    |

|---|---|---|---|---|---|---|----|-----|---|---|----|------|-----|-----|----|----|

|   | 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10 | 11   | 12  | 13  | 14 | 15 |

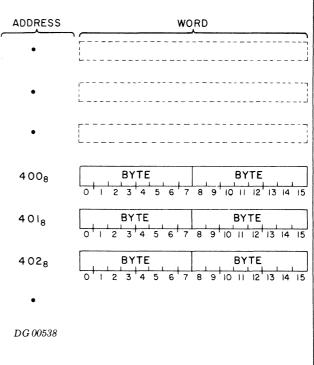

Bit 5 is called the *indirect bit*, bits 6 and 7 are called the index bits, and bits 8-15 are called the displacement bits.

If the index bits are 00, the displacement is used as an unsigned 8-bit number to address one of the first  $256_{10}$ words in memory. This is called *page zero addressing* and this first block of 256 words is known as page zero.

If the index bits are 01, the displacement is treated as a signed, two's complement number, which is added to the address of the instruction to produce a memory address. This is called *relative addressing*. By relative addressing, any instruction which uses the effective address calculation can directly address any word in

#### INTERNAL STRUCTURE

storage whose address is in the range  $-128_{10}$  to  $+127_{10}$  from the instruction.

If the index bits are 10, accumulator 2 is used as an index register. If the index bits are 11, accumulator 3 is used as an index register. In this form of word addressing, known as *index register addressing*, the displacement is treated as a signed, two's complement number which is added to the contents of the selected index register to produce a memory address. In index register addressing, the addition of the displacement to the contents of index register does not change the value contained in the index register.

The result of the addition performed in relative addressing and index register addressing is *clipped* to 15 bits. In other words, the high order bit of the result is set to 0. For example, if accumulator 2 is to be used as an index register and contains the number  $077774_8$ , and the displacement bits contain the number  $012_8$ , then the result of the addition would be  $000006_8$ , not  $100006_8$ .

After one of the three types of addresses has been computed from the index and displacement bits, the indirect bit is tested. If this bit is zero, the address already computed is taken as the effective address. If the indirect bit is one, the word addressed by the result of the index and displacement bits is assumed to contain an address. In this word bit 0 is the indirect bit and bits 1-15 contain an address. If bit 0 of the referenced word is 1, another level of indirection is indicated, and bits 1-15 contain the address of the next word in the indirection chain. The processor will continue to follow this chain of indirect addresses until a word is retrieved with bit 0 set to 0. Bits 1-15 of this word are taken to be the effective address.

#### Auto-Increment/Decrement

If an indirect address points to a location in the range  $20-27_8$  (auto-increment locations); that word is fetched, the contents of the word are incremented by one and written back into the location. This updated value is then used to continue the addressing chain. If an indirect address points to a location in the range  $30-37_8$  (auto-decrement location), that word is fetched, the contents of the word are decremented by one and written back into the location. The updated value is then used to continue the addressing chain.

NOTE: When referencing auto-increment and auto-decrement locations, the state of bit 0 before the increment or decrement is the condition upon which the continuation of the indirection chain is based. For example: if an auto-increment location contains  $177777_8$ , and the location is referenced as part of an indirection chain, location 0 will be the next address in the chain.

An effective address is always 15 bits in length. This means that an instruction which uses the effective address calculation can address any one of  $32,768_{10}$  words. This gives rise to the concept of an *address space*, which, in the NOVA 4, contains 64K bytes or 32,768 2-byte words.

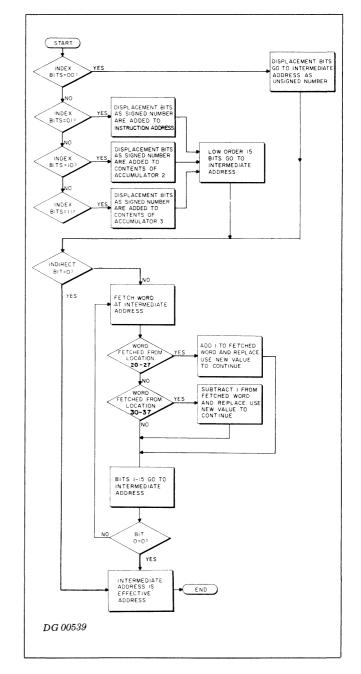

## **Byte Addressing**

While bytes in main memory cannot be directly addressed by the CPU, there is a convenient programming method for manipulating individual bytes of information. This technique involves the use of a *byte pointer*. A byte pointer is a word in which bits 0-14 are the address in memory of a 2-byte word. Bit 15 is the *byte indicator*. If the byte indicator is 0, the byte pointer references the high-order byte (bits 0-7) of the word in memory; if it is 1, the pointer references the low order byte (bits 8-15).

# Addressing With Address Translation Hardware

The concept of an address space was introduced in the discussion of effective address calculation. The *program* or *logical* address space is that amount of memory that can be referenced by instructions in a program. The maximum logical address space available to a program running on a NOVA 4 is 64K bytes or 32K words.

The physical address space is that amount of physical memory that can be referenced by the CPU. If the MAP is not installed, the maximum physical address space available to the CPU is 64K bytes or 32K words, and the logical address space is equal to the physical space. For a NOVA 4 with the MAP installed, the maximum physical address space is 256K bytes and the logical address space is some subset of the physical space.

Installation of a MAP has no effect on logical addressing. Addressing calculations remain the same. The MAP translates the 15-bit address from the CPU into a 17-bit address and uses this new address to perform the memory reference.

# **PROGRAM EXECUTION**

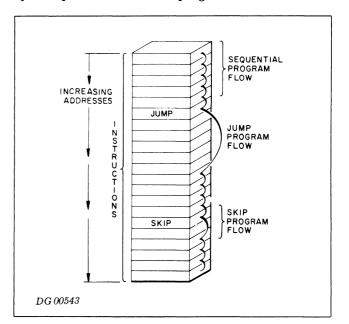

Programs for the NOVA 4 consist of sequences of instructions that reside in main memory. The order in which these instructions are executed depends on a 15-bit counter called the *program counter*. The program counter always contains the address of the instruction currently being executed. After the completion of each instruction, the program counter is incremented by one and the next instruction is fetched from this address. This is called *sequential operation*, and the instruction fetched from the location addressed by the incremented program counter is called the *next sequential instruction*.

# **Program Flow Alteration**

Sequential operation can be explicitly altered by the programmer in two ways: jump instructions alter program flow by inserting a new value into the program counter: conditional skip instructions can alter program flow by incrementing the program counter an extra time if a specified test condition is true. In the case of a conditional skip instruction, when the test condition is true, the next sequential instruction is not executed because it is not addressed. After either a jump instruction, sequential operation continues with the instruction, sequential by the updated value of the program counter.

Because the program counter is 15 bits in length, it can address 32,768 separate memory locations. The next memory location after  $77777_8$  is location 0, and the location before 0 is location  $77777_8$ . If the program counter rolls from  $77777_8$  to 0 in the course of sequential operation, no indication is given and processing continues with the location addressed by the updated value of the program counter.

INTERNAL STRUCTURE

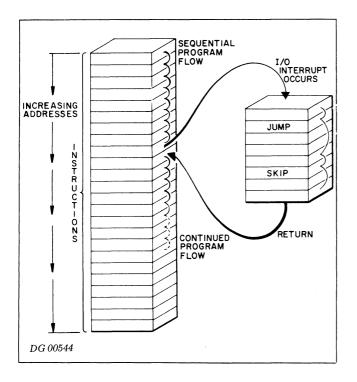

# **Program Flow Interruption**

The normal flow of a program may be interrupted by external or exceptional conditions such as I/O interrupts or various kinds of faults. In this case, the address of the next sequential instruction in the interrupted program is saved by the CPU so that the I/O handler, or the various fault handlers, can return control to the program at the correct point. Once the address of the next sequential instruction in the program has been placed in the program counter by the fault handler, sequential operation of the program resumes.

# Chapter III INSTRUCTIONS SETS

# INTRODUCTION

The instruction set implemented on the NOVA 4 is divided into 5 sets. There are instruction sets available for fixed point arithmetic, logical operations, program flow alteration, floating point arithmetic, and I/O operations. In addition, instructions are available for programming the stack, MAP, the Real Time Clock, power fail/auto-restart, and certain CPU functions.

# **INSTRUCTION FORMATS**

There are four different formats for instructions on the NOVA 4. These formats allow an extensive instruction set while still keeping the instruction length to one word. The four formats and their general layouts are described below.

| 0 | 0 | 0 | OF | 'N | @ |   |   |   |   |    | ISPL | ACE | MEN | ŗ  |    |

|---|---|---|----|----|---|---|---|---|---|----|------|-----|-----|----|----|

| 0 | 1 | 2 | 3  | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12  | 13  | 14 | 15 |

In the No Accumulator-Effective Address format instructions, bits 0-2 are 000, and bits 3-4 contain the operation code. The effective address is computed from bits 5-15 as described under *Effective Address Calculation*.

In the One Accumulator-Effective Address format instructions, bit 0 is 0, and bits 1-2 contain the operation code. Bits 3-4 specify the accumulator for the operation. The effective address is computed from bits 5-15 as described under *Effective Address Calculation*.

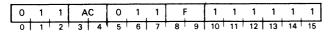

| Γ | 0 | 1 | 1 | Α | С | 0 | OP CODE |   | F |   |    | DEVICE CODE |    |    |    |    |

|---|---|---|---|---|---|---|---------|---|---|---|----|-------------|----|----|----|----|

| - | 0 | 1 | 2 | 3 | 4 | 5 | 6       | 7 | 8 | 9 | 10 | 11          | 12 | 13 | 14 | 15 |

In the Input/Output format instructions, bits 0-2 are

001, bits 3-4 specify the accumulator for the operation, bits 5-7 contain the operation code, bits 8-9 specify the control signal to be used, and bits 10-15 contain the device code of the referenced device.

| 1 |   | NCS | S | A | CD | 0 |   |   | s | н | c  |    | #  |    | SKIP |    |

|---|---|-----|---|---|----|---|---|---|---|---|----|----|----|----|------|----|

| 0 | 1 | +   | 2 | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

In the Arithmetic/Logical Class instructions, bit 0 is 1, bits 1 and 2 specify the source accumulator, bits 3 and 4 specify the destination accumulator, bits 5-7 contain the operation code, bits 8 and 9 specify the action of the shifter, bits 10 and 11 specify the value to which the carry bit will be initialized, bit 12 specifies whether or not the result will be loaded into the destination accumulator, and bits 13-15 specify the skip test.

# **ALC Instruction Execution**

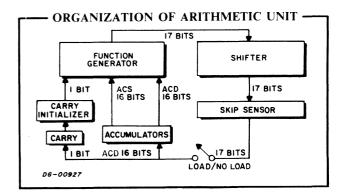

The ALC instructions use an Arithmetic Logic Unit (ALU) to process data. The logical organization of the ALU is illustrated below.

When an ALC instruction begins execution, it loads the contents of the carry bit and the contents of the accumulator(s) to be processed into the ALU. There are five distinct stages of ALU operation. We will discuss these stages separately.

#### Carry

The ALU begins its manipulation of the data by determining a new value for the carry bit. This new value is based upon three things: the old value of the carry, bits 10-11 of the ALC instruction, and the ALC instruction being executed. The ALU first determines the effect of the instruction bits 10-11 on the old value of the carry. The table below shows each of the mnemonics that can be appended to the instruction mnemonic, the value of bits 10-11 for each choice, and the action each one takes.

| SYMBOL        | VALUE | OPERATION                                              |

|---------------|-------|--------------------------------------------------------|

| [c] omitted   | 00    | Leave Carry bit unchanged<br>Initialize Carry bit to 0 |

| [c]= <b>O</b> | 10    | Initialize Carry bit to 1                              |

| [c]=C         | 11    | Complement the Carry bit                               |

#### Function

The ALU next evaluates the effect of the specific function (bits 5-7) upon the data. For the instructions *Move, AND,* and *Complement* the ALU performs the function on the data word(s) and saves the result. The value of the carry is as it was calculated above. For the instructions *Add, Add Complement, Subtract, Negate,* and *Increment* the result of the function's action upon the data word(s) may be larger than  $2^{16}$ -1. A carry out results. In this situation, the ALU saves the low-order 16 bits of the function result, but it complements the value of the carry calculated above.

NOTE: At this stage of operation, the ALU does not load either the saved value of the function result into the destination accumulator, or the saved value of the carry into the carry bit.

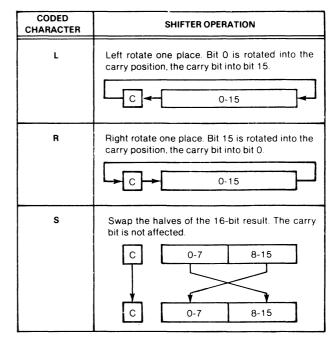

#### **Shift Operations**

Next the ALU performs any specified shift operation on the 17 bits output from the function generator (16 bits of data plus the calculated value of the carry bit). Depending on which shift operation is specified in the instruction, the function generator output can be rotated left or right one bit, or have its bytes swapped. The first table below shows the different shift operations that can be performed, the value of bits 8-9 for each choice, and the action each choice takes. The second table shows how each shift operation works.

| SYMBOL       | VALUE | OPERATION                                                                               |

|--------------|-------|-----------------------------------------------------------------------------------------|

| [sh] omitted | 00    | Do not shift the result of the ALC operation                                            |

| [sh]=L       | 01    | Rotate left the 17-bit<br>combination of Carry bit<br>and ALC operation result          |

| [sh]=R       | 10    | Rotate right the 17-bit<br>combination of Carry bit<br>and ALC operation result         |

| [sh]=s       | 11    | Swap the two 8-bit halves<br>of the ALC operation result<br>without affecting Carry bit |

DG 04423

#### **Skip Tests**

The ALU can test the result of the shift operation for one of a variety of conditions, and skip or not skip the next instruction depending upon the result of the test. The table below shows the tests that can be performed, the value of bits 13-15 for each choice, and the action each choice takes.

#### **INSTRUCTIONS SETS**

| SYMBOL                                                                                                           | VALUE                                                | OPERATION                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [skip] omitted<br>[skip]=SKP<br>[skip]=SZC<br>[skip]=SNC<br>[skip]=SZR<br>[skip]=SNR<br>[skip]=SEZ<br>[skip]=SBN | 000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | No skip<br>Skip unconditionally<br>Skip if Carry bit is zero<br>Skip if Carry bit is nonzero<br>Skip if ALC result is zero<br>Skip if ALC result is nonzero<br>Skip if either ALC result<br>or Carry bit is zero<br>Skip if both ALC result<br>and Carry bit is nonzero |

|                                                                                                                  |                                                      | and Carry bit is nonzero                                                                                                                                                                                                                                                |

#### Load/No-Load

If the no-load bit (bit 12) is 0, the ALU loads the result of the shift operation into the destination accumulator, and loads the new value of the carry into the carry bit. If the no-load bit is 1, then the ALU does not load the result of the shift operation into the destination accumulator, and does not load the new value of the carry into the carry bit, but all other operations, such as skip tests, take place. This no-load option is particularly convenient to use when you want to test for some condition without destroying the contents of the destination accumulator. The table below shows how to code the load/no-load operation.

| SYMBOL    | VALUE | OPERATION                                                                                                 |

|-----------|-------|-----------------------------------------------------------------------------------------------------------|

| # omitted | 0     | Load the result of the shift operation into ACD                                                           |

| #         | 1     | Do not load the ALC<br>operation result into ACD;<br>restore Carry bit to value<br>it had before shifting |

NOTE: These instructions must not have both the No-Load and the Never-Skip options specified at the same time. These bit combinations are used by other instructions in the instruction set.

As an example of how to use these tables, assume that accumulator 3 contains a signed, two's complement number. Now consider the problem of determining whether this number is positive or negative. One way to determine this would be to place the number zero in another accumulator and use the Subtract instruction, but this requires an extra instruction and also destroys the previous contents of the other accumulator. Another way to determine the sign of the number in accumulator 3 is to use the Move instruction and power of the two accumulator-multiple operation format. With the Move instruction, the contents of AC3 can be placed in the shifter and shifted one bit to the left. This places the sign bit in the carry bit. The carry bit can then be tested for zero. In order to preserve the number in AC3, the instruction can prevent the

output of the shifter from being loaded back into AC3.

The general form of the *Move* instruction is:

# **MOV**[c][sh][#] acs,acd[,skip]

The general bit pattern of the MOVE instruction is:

| Γ | 1 | A | cs | A | CD | 0 | 1 | 0 | S | н | C  | 2  | #  |    | SKIP |    |

|---|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

|   | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

To shift the number in AC3 one bit left without destroying the number, and skip the next sequential instruction if the bit shifted into the carry bit is zero, the following instruction could be coded:

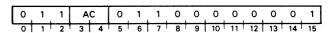

#### MOVL# 3,3,**SZC**

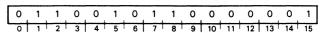

This instruction assembles into the following bit pattern:

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    | 0  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

# **CODING AIDS**

We use certain conventions and abbreviations throughout this chapter to help you properly code each instruction for Data General's assembler. Briefly, they are these:

- [] [] Square brackets indicate that the enclosed symbol (e.g., *l,skipl*) is an optional operand or mnemonic. Code it only if you want to specify the option.

- **BOLD** Code operands or mnemonics printed in boldface exactly as shown. For example, code the mnemonic for the *Move* instruction: MOV.

- *italic* For each operand or mnemonic in italics, replace the item with a number or symbol that provides the assembler value you need for that item (e.g., the proper accumulator number, an address, etc.).

We use the following abbreviations throughout this chapter:

| ABBR | MEANING                    |

|------|----------------------------|

| AC   | Accumulator                |

| ACS  | Source accumulator         |

| ACD  | Destination accumulator    |

| FPAC | Floating point accumulator |

In the instructions that use an effective address, the following coding conventions are used:

The indirect bit (bit 5) is set to 1 by coding the symbol @ anywhere in the effective address operand string.

The index bits are set by coding a comma followed by one of the digits 0-3 as the last operand of the operand string. If no index is coded, the bits are set to 00. The character *period* (.) can be used to set the index bits to 01. *Period* can be read to mean *address of the current instructions*. When the period is used, it is followed by either a plus or a minus sign followed by the displacement e.g., .+7, or .-2.

The displacement is coded as a signed number in the current assembler radix. This radix is the numbering system in which the programmer supplies numbers to the assembler. The default radix is Base 8 or octal. The assembler radix can be changed by using the RADIX statement.

The assembler available with the NOVA 4 allows the programmer to place labels on instructions or locations in memory. When the assembler comes upon a label in the operand string of an effective address instruction, it automatically sets the index and displacement bits to the correct values.

# FIXED POINT ARITHMETIC

The fixed point instruction set performs binary arithmetic on operands in accumulators. The operands are 16 bits in length and can be either signed or unsigned. The instruction set provides for loading, storing, adding, and subtracting.

## Load Accumulator

## LDA *ac,[@]displacement[,index]*

| [ | 0 | 0 | 1 | AC |   | @ | INDE | X |   |   | DIS | SPLA | CEM | ENT |    |    |

|---|---|---|---|----|---|---|------|---|---|---|-----|------|-----|-----|----|----|

|   | 0 | 1 | 2 | 3  | 4 | 5 | 6    | 7 | 8 | 9 | 10  | 11   | 12  | 13  | 14 | 15 |

Copies a word from memory to an accumulator.

Places the word addressed by the effective address, E, in the specified accumulator. The previous contents of the location addressed by E remain unchanged.

## **Store Accumulator**

#### **STA** *ac,[@]displacement[,index]*

| 0 | 1 | 0 | Ι   | AC | 2 | @ | IN | DEX |    |   | D  | ISPL | ACE | MENT | Г  |    |

|---|---|---|-----|----|---|---|----|-----|----|---|----|------|-----|------|----|----|

| 0 | 1 | 2 | 1 3 | Т  | 4 | 5 | 6  | 7   | 18 | 9 | 10 | 11   | 12  | 13   | 14 | 15 |

Stores the contents of an accumulator into a memory location.

Places the contents of the specified accumulator in the word addressed by the effective address, E. The previous contents of the location addressed by E are lost. The contents of the specified accumulator remain unchanged.

# Subtract

## SUB[c][sh][#] acs,acd[,skip]

| 1 | A | cs | A | CD | 1 | 0 | 1 | S | н | C  | 2  | #  |    | SKIP |    |

|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

| 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Performs unsigned integer subtraction and complements the carry bit if appropriate.

Initializes the carry bit to its specified value. The instruction subtracts the unsigned, 16-bit number in ACS from the unsigned, 16-bit number in ACD by taking the two's complement of the number in ACS and adding it to the number in ACD. The instruction places the result of the addition in the shifter. If the operation produces a carry of 1 out of the high-order bit, the instruction complements the carry bit. The instruction performs the specified shift operation and places the result of the shift in ACD if the no-load bit is 0. If the skip condition is true, the instruction skips the next sequential word.

NOTE: If the number in ACS is less than or equal to the number in ACD, the instruction complements the carry bit.

# Add

ADD[c][sh][#] acs,acd[,skip]

| ſ | 1 | A | cs | A | CD | 1 | 1 | 0 | S | н | C  | :  | #  |    | SKIP |    |

|---|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

|   | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Performs unsigned integer addition and complements the carry bit if appropriate.

Initializes the carry bit to the specified value, adds the unsigned, 16-bit number in ACS to the unsigned, 16-bit number in ACD, and places the result in the shifter. If the addition produces a carry of 1 out of the high-order bit, the carry bit is complemented. The instruction then performs the specified shift operation and places the result of the shift in ACD if the no-load bit is 0. If the skip condition is true, the next sequential word is skipped.

NOTE: If the sum of the two numbers being added is greater than 65,535, the instruction complements the Carry bit.

## Negate

NEG[c][sh][#] acs,acd[,skip]

| 1 | ACS | ACD | 0 | 0 | 1 | SH  | Ç     | #  | SKIP    |   |

|---|-----|-----|---|---|---|-----|-------|----|---------|---|

| 0 | 1 2 | 3 4 | 5 | 6 | 7 | 8 9 | 10 11 | 12 | 13 14 1 | 5 |

Forms the two's complement of the contents of an accumulator.

Initializes the carry bit to the specified value. Places the two's complement of the unsigned, 16-bit number in ACS in the shifter. If the negate operation produces a carry of 1 out of the high-order bit, the instruction complements the carry bit. Performs the specified shift operation and places the result in ACD if the no-load bit is 0. If the skip condition is true, the instruction skips the next sequential word.

**NOTE:** If ACS contains 0, the instruction complements the carry bit.

# Add Complement

# ADC[c][sh][#] acs,acd[,skip]

| Γ | 1 | Α | çs | 5 | A | CD | 1 | 0 | 0 | s | н | C  | :  | #  |    | SKIP |    |

|---|---|---|----|---|---|----|---|---|---|---|---|----|----|----|----|------|----|

|   | 0 | 1 | t  | 2 | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Adds an unsigned integer to the logical complement of another unsigned integer.

Initializes the carry bit to the specified value, adds the logical complement of the unsigned, 16-bit number in ACS to the unsigned, 16-bit number in ACD, and places the result in the shifter. If the addition produces a carry of 1 out of the high-order bit, the carry bit is complemented. The instruction then performs the specified shift operation, and loads the result of the shift into ACD if the no-load bit is 0. If the skip condition is true, the next sequential word is skipped.

NOTE: If the number in ACS is less than the number in ACD, the instruction complements the Carry bit.

#### **Data General Corporation**

## Increment

INC[c][sh][#] acs,acd[,skip]

| ſ | 1 | A | cs | A | ÇD | 0 | 1 | 1 | S | н | C  | :  | #  |    | SKIP |    |

|---|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

|   | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Increments the contents of an accumulator.

Initializes the carry bit to the specified value. Increments the unsigned, 16-bit number in ACS by one and places the result in the shifter. If the incrementation produces a carry of 1 out of the high order bit, the instruction complements the carry bit. Performs the specified shift operation, and loads the result of the shift into ACD if the no-load bit is 0. If the skip condition is true, the next sequential word is skipped.

NOTE: If the number in ACS is  $177777_8$  the instruction complements the carry bit.

## Move

MOV[c][sh][#] acs,acd[,skip]

| Γ | 1 | Α | cs | A | CD | 0 | 1 | 0 | S | н | 0  |    | #  |    | SKIP |    |

|---|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

|   | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Moves the contents of an accumulator through the Arithmetic Logic Unit (ALU).

Initializes the carry bit to the specified value. Places the contents of ACS in the shifter. Performs the specified shift operation and loads the result of the shift into ACD if the no-load bit is 0. If the skip condition is true, the instruction skips the next sequential word.

# LOGICAL OPERATIONS

The logical instruction set performs logical operations on operands in accumulators. The operands are 16 bits long and are treated as unstructured binary quantities. The logical operations included in this set are: And, and Complement.

# AND

AND[c][sh][#] acs,acd[,skip]

| ſ | 1 | 4 | ١Ċ | s |   | A | CD |   | 1 | 1   | 1 | T | S | н |   | C  |    | #  | 1  |    | SKIP |    |

|---|---|---|----|---|---|---|----|---|---|-----|---|---|---|---|---|----|----|----|----|----|------|----|

|   | 0 | 1 | 1  | 2 | T | 3 | 4  | 1 | 5 | 6 T | 7 | T | 8 | 9 | 1 | 10 | 11 | 12 | 21 | 13 | 14   | 15 |

Forms the logical AND of the contents of two accumulators.

Initializes the carry bit to the specified value and places the logical AND of ACS and ACD in the shifter. Each bit placed in the shifter is 1 only if the corresponding bit in both ACS and ACD is one; otherwise the resulting bit is 0. The instruction then performs the specified shift operation and places the result in ACD if the no-load bit is 0. If the skip condition is true, the next sequential word is skipped.

## Complement

COM[c][sh][#] acs,acd[,skip]

| Γ | 1 | A | cs | A | ÇD | 0 | 0 | 0 | S | н | C  | 2  | #  |    | SKIP |    |

|---|---|---|----|---|----|---|---|---|---|---|----|----|----|----|------|----|

| - | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14   | 15 |

Forms the logical complement of the contents of an accumulator.

Initializes the carry bit to the specified value, forms the logical complement of the number in ACS, and performs the specified shift operation. The instruction then places the result in ACD if the no-load bit is 0. If the skip condition is true, the next sequential word is skipped.

# **STACK MANIPULATION**

An important feature of the NOVA 4 is the stack manipulation facility. A Last-In/First-Out (LIFO) or *Push-Down* stack is maintained by the processor. The stack facility provides an expandable area of temporary storage for variables, data, return addresses, subroutine arguments, etc. An important byproduct of the stack facility is that storage locations are reserved only when needed. When a procedure is finished with its portion of the stack, those memory locations are reclaimed and are available for use by some other procedure.

The operation of the stack depends upon the contents of two hardware registers. The registers and their contents are described below.

# **Stack Pointer**

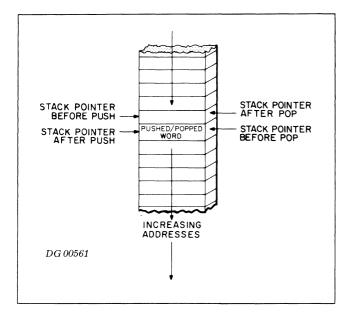

The stack pointer is the address of the *top* of the stack and is affected by operations that either *push* objects onto or *pop* objects off the stack. A push operation increments the stack pointer by 1 and then places the *pushed* object in the word addressed by the new value of the stack pointer. A pop operation takes the word addressed by the current value of the stack pointer and places it in some new location and then decrements the stack pointer by 1.

# **Frame Pointer**

The frame pointer is used to reference an area in the user stack called a *frame*. A frame is that portion of the stack which is reserved for use by a certain procedure. The frame pointer usually points to the first available word minus 1 in the current frame. The frame pointer is also used by the *Return*  instruction to reset the user stack pointer. **Return Block**

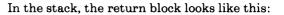

A return block is defined as a block of five words that is pushed onto the stack in order to allow convenient return to the calling program. The format of the return block, therefore, is determined by how it is used in the return sequence. The format of the return block is as follows:

| WORD POPPED | DESTINATION                                                                      |

|-------------|----------------------------------------------------------------------------------|

| 1           | Bit O placed in the<br>carry bit.<br>Bits 1-15 placed in<br>the program counter. |

| 2           | AC3                                                                              |

| 3           | AC2                                                                              |

| 4           | AC1                                                                              |

| 5           | ACO                                                                              |

|             |                                                                                  |

# **Stack Frames**

In order to implement re-entrant subroutines, a new area of temporary storage must be available for each execution of a called subroutine. The easiest way to accomplish this is for the subroutine to use the stack for temporary storage. A *stack frame* is defined as that portion of the stack which is available to the called routine. In general, the stack frame belonging to a subroutine begins with the first word in the stack after the return block pushed by the called routine and contains all words in the stack up to, and including, the return calls. Variables and arguments can be transmitted from the calling routine to the called routine by placing them in prearranged

#### INSTRUCTIONS SETS

positions in the stack frame of the calling routine. Because the *Save* instruction sets the frame pointer to the last word in the return block, these variables and arguments can be referenced by the called program as a negative displacement from the frame pointer. The called routine should ensure that reference to the stack frome of the calling routine is made only with the permission of the calling routine.

#### **Stack Protection**

During every instruction that pushes data onto the stack, a check is made for stack overflow. If the instruction places data in a word whose address is an integral multiple of  $256_{10}$ , a stack overflow is indicated. If a stack overflow is indicated, the instruction is completed, an internal stack overflow flag is set to 1, and, if the Interrupt On flag is 1, a stack fault is performed. If the Interrupt On flag is 0, the stack overflow flag remains set to 1, and as soon as the interrupt system is enabled, the stack fault is performed.

When a stack fault is performed: if a program map is enabled, it is inhibited; the Interrupt On flag is set to 0; the stack overflow play is set to 0; the updated program counter is stored in physical location 0; and the processor executes a *jump indirect* to physical location 3.

#### Initialization of the Stack Control Registers

Before the first operation on the stack can be performed, the stack control registers must be initialized. The rules for initialization are as follows:

#### Stack Pointer

The stack pointer must be initialized to the beginning address of the stack area minus one.

#### Frame Pointer

If the main user program is going to use the frame pointer, it should be initialized to the same value as the stack pointer. Otherwise, the frame pointer can be initialized in a subroutine by the *Save* instruction.

# STACK MANIPULATION INSTRUCTIONS

The stack feature of the NOVA 4 computer is programmed with eight I/O instructions which use the device code 01. Although the instructions are in the standard I/O format, the operation of these instructions is in no way similar to I/O instructions.

## **Push Accumulator**

PSHA ac

Pushes the contents of the specified accumulator onto the stack, and increments the stack pointer by one.

# **Pop Accumulator**

## POPA ac

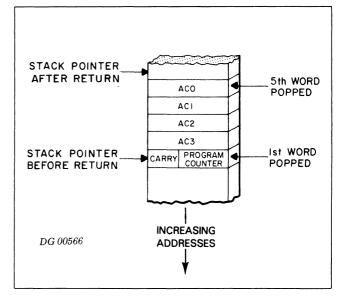

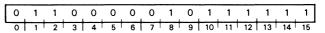

| 0 | 1 | 1 | A | С | 0 | 1 | 1 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Pops 1 word off the stack, places it in the indicated accumulator, and decrements the stack pointer by one.

# **Move To Stack Pointer**

## MTSP ac

|   | 1 | 1 | A | с | 0 | 1 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places bits 1-15 of the specified accumulator in the stack pointer. The contents of the specified accumulator remain unchanged.

# Save

# SAV

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Pushes a return block onto the stack. After the fifth word of the return block is pushed, the value of the stack pointer is placed in the frame pointer and in AC3. The format of the five words pushed is as follows:

| WORD PUSHED           | CONTENTS                                                                                                |

|-----------------------|---------------------------------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5 | AC0<br>AC1<br>AC2<br>Frame pointer before the save<br>Bit 0 = carry bit<br>Bits 1-15 = bits 1-15 of AC3 |

## **Move To Frame Pointer**

#### MTFP ac

| 0 | 1 | 1 | A | С | 0 | 0 | 0 | 0 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   |   |   |   | 1 |   |   | L | _ |   | I  | L  | _  |    |    |    |

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places bits 1-15 of the specified accumulator in the frame pointer. The contents of the specified accumulator remain unchanged.

## **Move From Stack Pointer**

#### MFSP ac

| ſ | 0 | 1 | 1 |     | A | с | 0 | 1 | 0 | 1 | 0 | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|-----|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   | 0 | 1 | 2 | 1 3 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places the contents of the stack pointer in bits 1-15 of the specified accumulator. Sets bit 0 of the accumulator to 0. The contents of the stack pointer remain unchanged.

# **PROGRAM FLOW ALTERATION**

As stated previously, the normal method of program execution is sequential. That is, the processor will continue to retrieve instructions from sequentially addressed locations in memory until directed to do otherwise. Instructions are provided in the instruction set that alter this sequential flow. Program flow alteration is accomplished by placing a new value in the program counter. Sequential operations will then continue with the instruction addressed by this new value. Instructions are provided that change the value of the program counter, change the value of the program counter and save a return address, or modify a memory location by incrementing or decrementing and skip the next sequential instruction if the result is zero.

#### **Move From Frame Pointer**

#### MFFP ac

| - |   |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

|   |   |   |   |   |   |   |   |   |   |    |    |    |    |    | 1  |

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Places the contents of the frame pointer in bits 1-15 of the specified accumulator. Sets bit 0 of the accumulator to 0. The contents of the specified accumulator remain unchanged.

#### JMP

| Γ | 0 | 0 | 0 | 0 | 0 | @ | IN | DEX |   |   | D  | ISPL | ACE | MEN | Γ  |    |

|---|---|---|---|---|---|---|----|-----|---|---|----|------|-----|-----|----|----|

| _ | 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10 | 11   | 12  | 13  | 14 | 15 |

Computes the effective address, *E*, and places it in the program counter. Sequential operation continues with the word addressed by the updated value of the program counter.

**Data General Corporation**

## **Jump To Subroutine**

#### JSR [@]displacement[,index]

| 0 | 0 | 0 | 0 | 1 | @ | IN | DEX |   |   | D  | ISPL | ACE | MENT | ŗ  | _  |

|---|---|---|---|---|---|----|-----|---|---|----|------|-----|------|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10 | 11   | 12  | 13   | 14 | 15 |

Increments and stores the value of the program counter in AC3, and then places a new address in the program counter.

Computes the effective address, E; then places the address of the next sequential instruction in AC3. Places E in the program counter. Sequential operation continues with the word addressed by the updated value of the program counter.

NOTE: The instruction computes E before it places the incremented program counter in AC3.

## **Decrement And Skip If Zero**

DSZ [@]displacement[,index]

| 0 | 0 | 0 | 1 | 1 | @ | IN | DEX | I |   | D  | ISPL | ACE | MENT | Г  |    |

|---|---|---|---|---|---|----|-----|---|---|----|------|-----|------|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6  | 7   | 8 | 9 | 10 | 11   | 12  | 13   | 14 | 15 |

Decrements the addressed word, then skips if the decremented value is zero.

Decrements by one the word addressed by E and writes the result back into that location. If the updated value of the location is zero, the instruction skips the next sequential word.

## **Increment And Skip If Zero**

| ISZ [@]displacement[,index] |  |

|-----------------------------|--|

|-----------------------------|--|

| 0 |   |   |   |   |   |   | DEX |   |   |    |    |    | MENT |    |    |   |

|---|---|---|---|---|---|---|-----|---|---|----|----|----|------|----|----|---|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7   | 8 | 9 | 10 | 11 | 12 | 13   | 14 | 15 | • |

Increments the addressed word, then skips if the incremented value is zero.

Increments the word addressed by E and writes the result back into memory at that location. If the updated value of the location is zero, the instruction skips the next sequential word.

### Return

#### RET

Places the contents of the frame pointer in the stack pointer and pops five words off the stack, placing them in the following locations:

| WORD # POPPED | DESTINATION                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------|

| 1             | Bit O placed in the<br>carry bit.<br>Bits 1-15 placed in                                        |

| 2             | the program counter.<br>Bits 1-15 placed in<br>the frame pointer.<br>Bits 0-15 placed in<br>AC3 |

| 3             | AC2                                                                                             |

| 4             | AC1                                                                                             |

| 5             | ACO                                                                                             |

Sequential operation continues with the word addressed by the updated value of the program counter.

Trap

#### **TRAP** acs, acd, trap number

| Γ | 1 | A | çs | A | CD |   |   | TF | APN | NUM | BER |    | 1  | 0  | 0  | 0  |

|---|---|---|----|---|----|---|---|----|-----|-----|-----|----|----|----|----|----|

|   | 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7  | 8   | 9   | 10  | 11 | 12 | 13 | 14 | 15 |

Disables the user map if enabled. Then places the logical address of this instruction in bits 1-15 of physical location  $46_8$ , sets bit 0 of this location to 0, and jumps indirect via location  $47_8$ . The state of the Interrupt On flag is unaltered.

# **BYTE INSTRUCTIONS**

The following instructions move bytes to or from memory locations. Note that when an instruction moves a byte from memory to an accumulator, it also clears the high-order half of the destination accumulator. When an instruction moves a byte from an accumulator to memory, it leaves unchanged the other byte contained in that word of memory.

#### Load Byte

LDB acs, acd

| 0 | 1 | 1 | A | CD | 0 | 0 | 1 | A | cs | 0  | 0  | 0  | 0  | 0  | 1  |

|---|---|---|---|----|---|---|---|---|----|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4  | 5 | 6 | 7 | 8 | 9  | 10 | 11 | 12 | 13 | 14 | 15 |

Moves a byte from memory (as addressed by a byte pointer in one accumulator) to the second accumulator.

Places the 8-bit byte addressed by the byte pointer contained in ACS in bits 8-15 of ACD. Sets bits 0-7 of ACD to 0. The contents of ACS remain unchanged unless ACS and ACD are the same accumulator.

# **Store Byte**

## STB acs, acd

|   |   | 1 |   | 1 |   | 1 |   | ACS |   |    |    |    |    |    | 1  |

|---|---|---|---|---|---|---|---|-----|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8   | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Moves the right byte of one accumulator to a byte in memory. The second accumulator contains the byte pointer.

Places bits 8-15 of ACD in the byte addressed by the byte pointer contained in ACS. The contents of ACS and ACD remain unchanged.

# Chapter IV INPUT/OUTPUT

# INTRODUCTION

In order for the processor to perform useful work for the user, there must be some method for the program to transfer information outside the machine. The Input/Output (I/O) instruction set provides this facility. There are eight I/O instructions which allow the program to communicate with I/O devices, control certain processor options, and perform certain processor functions.

The NOVA 4 has a 6-bit device selection network, corresponding to bits 10-15 in the I/O instruction format. Each device is connected to this network in such a way that each device will only respond to commands with its own device code. Each device also has two flags, Busy and Done, which control its operation. When Busy and Done are both 0, the device is idle and cannot perform any operations. To start a device, the program must set Busy to 1 and set Done to 0. When a device has finished its operation, it sets Busy to 0 and Done to 1. The case of Busy and Done both set to 1 is a meaningless situation and will produce unpredictable results.

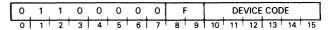

The format for the I/O instructions is illustrated below.

| 0 | 1 | 1 | A | C | OF | OP'N<br>5   6   7 |   |   |   | DE | VICE | CO | DE |    |    |

|---|---|---|---|---|----|-------------------|---|---|---|----|------|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5  | 6                 | 7 | 8 | 9 | 10 | 11   | 12 | 13 | 14 | 15 |

Bits 0-2 are 011, bits 3-4 specify the AC, bits 5-7 contain the operation code, bits 8-9 control the Busy and Done flags in the device, and bits 10-15 specify the code of the device. The six bits provided for the device code in the I/O format mean that 64 unique device codes are available for use. Some of these device codes, however, are reserved for the CPU and certain processor options. The remaining device codes are available for referencing I/O units. Some of the codes have been assigned to specific devices by Data General and the assembler recognizes mnemonics for these devices. A complete listing of device codes, the devices assigned to these codes, and the mnemonics assigned to the devices is available in Appendix A.

# **OPERATION OF I/O DEVICES**

In general, the operation of all I/O devices is done by manipulation of the Busy and Done flags. In order to operate a device, the program must first ensure that the device is not currently performing some operation. After the program has determined that the device is available, it can start an operation on the device by setting Busy to 1 and Done to 0. Once a device has completed its operation, and set Busy to 0 and Done to 1, it is available for another operation. The program can determine this condition in one of two ways. By using the I/O Skip instruction, the program can test the status of the Busy and Done flags. Another way is to use the interrupt system that is standard on the NOVA 4. The interrupt system is made up of an interrupt request line to which each I/O device is connected, an Interrupt On flag in the CPU, and a 16-bit interrupt priority mask. The Interrupt On flag controls the status of the interrupt system. If the flag is set to 1, the CPU will respond to and process interrupts. If the flag is set to 0, the CPU will not respond to any interrupts. An interrupt is initiated by an I/O device when it completes its operation.

Upon completing the operation, the device sets Busy to 0 and Done to 1. At this time, the device also places an interrupt request on the interrupt request line, provided that the bit in the interrupt priority mask which corresponds to the priority level of the device is 0. If the mask bit is 1, the device sets Busy to 0 and Done to 1, but does not place an interrupt request on the interrupt request line.

If the Interrupt On flag is 1 at the time the processor completes execution of any instruction, the processor honors any request on the interrupt request line. If the Interrupt On flag is 0, the CPU does not look at the interrupt request line; it just goes on to the next sequential instruction. The CPU honors an interrupt request by setting the Interrupt On flag to 0 so that no interrupts can interrupt the first part of the interrupt serivce routine. If no program map is enabled, the CPU places the updated program counter in physical memory location 0 and executes a *jump indirect* to physical memory location 1. It is assumed that location 1 contains the address, either direct or indirect, of the interrupt service routine. If the optional MAP is installed, it is inhibited; the updated program counter is placed in physical memory location 0 and the CPU executes a *jump indirect* to physical memory location 1.

Once the CPU has transferred control to the interrupt service routine, it is up to that routine to save any accumulators that will be used, save the carry bit if it will be used, determine which device requested the interrupt, and then service the interrupt. The determination of which device needs service can be done by *I/O Skip* instructions or the routine can use the *Interrupt acknowledge* instruction.

The Interrupt acknowledge instruction returns the 6-bit device code of the device requesting the interrupt. If more than one device is requesting service, the code returned is the code of that device requesting an interrupt which is physically closest to the CPU on the I/O bus. After servicing the device, the interrupt routine should restore all saved values, set the Interrupt On flag to 1, and return to the interrupted program. The instruction that sets the Interrupt On flag to 1 (Interrupt enable) allows the processor to execute one more instruction before the next interrupt can take place. In order to prevent the interrupt service routine from going into a loop, this next instruction should be the instruction that returns control to the interrupted program. Since the updated value of the program counter was placed in location 0 by the CPU upon honoring the interrupt, all the interrupt routine has to do, after restoring the AC's and the carry bit, is to execute an Interrupt enable instruction, a JMP 0 instruction, and control will be returned to the interrupted program.

# **PRIORITY INTERRUPTS**

If the Interrupt On flag remains 0 through the interrupt service routine, the interrupt routine cannot be interrupted and there is only one level of device priority. This level is determined by either the order in which the *I/O Skip* instructions are issued or (if *Interrupt Acknowledge* is used) by the physical location of the devices on the bus. In a system with devices of widely differing speed, such as a teletypewriter versus a fixed head disc, the programmer may wish to set up a multiple level interrupt scheme. Hardware and instructions are available that allow the implementation of sixteen levels of priority interrupts.

Each of the I/O devices is connected to a bit in the 16-bit priority mask. Devices which operate at roughly the same speed are connected to the same bit in the mask. Even though the standard mask bit assignments have the higher numbered bits assigned to lower speed devices, no implicit priority ordering is intended. The manner in which these priority levels are ordered is completely up to the programmer. The listing of device codes in Appendix A also contains the standard Data General mask bit assignments.

The condition of the priority mask is altered by the *Mask out* instruction. If a bit in the priority mask is set to 1, then all devices in the priority level corresponding to that bit will be prevented from requesting an interrupt when they complete an operation. In addition, all pending interrupt requests from devices in that priority level are disabled.

To implement a multiple priority level interrupt handler, the interrupt handler must be written in such a way that it may be interrupted without damage. For this to be possible, the main interrupt routine must save the state of the machine upon receiving control. The state of the machine consists of the four accumulators, the carry bit, and the return address. This information should be stored in a unique place each time the interrupt handler is entered so that one level of interrupt does not overlay the return information. The interrupt routine must determine which device requires service and jump to the correct service routine. This can be done in the same manner as for a single level interrupt handler.