**\***\*\*\*

4

1.2

あるま きんままく

Field Engineer's Maintenance Series

# NOVA<sup>®</sup>4/C

015-000097-01

n. A

Field Engineer's Maintenance Series

## DataGeneral

### NOTICE

Data General Corporation (DGC) has prepared this manual for use by DGC personnel and customers as a guide to the proper installation, operation, and maintenance of DGC equipment and software. The drawings and specifications contained herein are the property of DGC and shall neither be reproduced in whole or in part without DGC prior written approval nor be implied to grant any license to make, use, or sell equipment manufactured in accordance herewith.

DGC reserves the right to make changes without notice in the specifications and materials contained herein and shall not be responsible for any damages (including consequential) caused by reliance on the materials presented, including but not limited to typographical or arithmetic errors, company policy and pricing information. The information contained herein on DGC software is summary in nature. More detailed information on DGC software is available in current released publications.

NOVA, INFOS and ECLIPSE are registered trademarks of Data General Corporation, Westboro, Massachusetts. DASHER, microNOVA, and ECLIPSE MV/8000 are trademarks of Data General Corporation, Westboro, Massachusetts.

> Ordering No. 015-000097 \*Data General Corporation, 1979, 1980 All Rights Reserved Printed in the United States of America Rev. 01, December, 1980

**Field Engineer's Maintenance Series**

## PREFACE

This manual is a guide to troubleshooting and repairing NOVA 4/C computers at the field replaceable unit level, commonly referred to as "board swapping".

It is organized around four major sections.

Part 1 is a product description, which

- Introduces the major assemblies and explains how they interconnect

- Defines the field replaceable units

- Lists the related documentation

- Explains how to use the consoles.

Part 2 is devoted to troubleshooting. It explains both how to perform initial checkout and how to repair a system that failed after normal operation. It describes procedures for finding a failing field replaceable unit using:

- Visual checks

- The CPU's self-test feature

- Reliability and diagnostic test programs

- Simple manual tests.

These procedures, written in a "cookbook" manner, should allow the field engineer to repair most failures in a minimum period of time.

Part 3 contains reference information about the power supplies and the major printed circuit boards. This information is useful when you troubleshoot with an oscilloscope.

Part 4 provides detailed mechanical replacement procedures for each field replaceable unit.

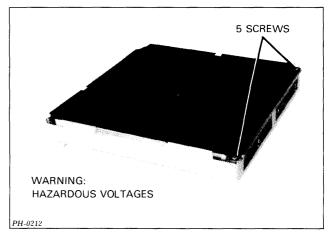

**WARNING:** The power supplies in these units have hazardous voltages on their printed circuit boards. They should be repaired only by trained service personnel.

# CONTENTS

Part 1 Product Description

1-3

2-5

3-3

3-11

3-19

Chapter 1 INTRODUCTION TO NOVA 4/C COMPUTERS

1-13 Chapter 2 HOW TO USE THE CONSOLES

Part 2 Troubleshooting

2-3 Chapter 3 INTRODUCTION TO TROUBLESHOOTING

Chapter 4 VISUAL CHECKOUT

2-7 Chapter 5 COMPUTER SELF-TEST

2-9 Chapter 6 TROUBLESHOOTING THE POWER SUPPLIES

2-17 Chapter 7 DIAGNOSTIC TESTING

2-31 Chapter 8 MANUAL TESTING

Part 3 Theory of Operation

Chapter 9 16-SLOT POWER SUPPLY OPERATION

Chapter 10 5-SLOT POWER SUPPLY OPERATION

Chapter 11 CPU OPERATION

## **Mechanical Replacement Procedures**

Chapter 12 REMOVING AND INSTALLING FRUS

**Appendices**

Part 4

Part 5

5-3

5-5

5-7

5-15

4-3

Appendix A RDOS PANIC CODES

Appendix B DTOS LOADING PROCEDURES

Appendix C FIELD SERVICE CASSETTE PROCEDURES

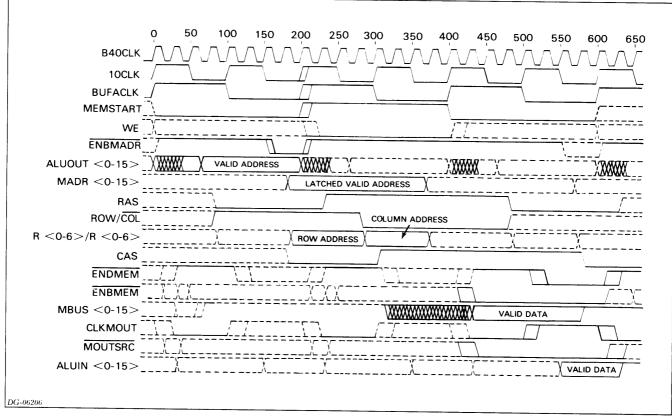

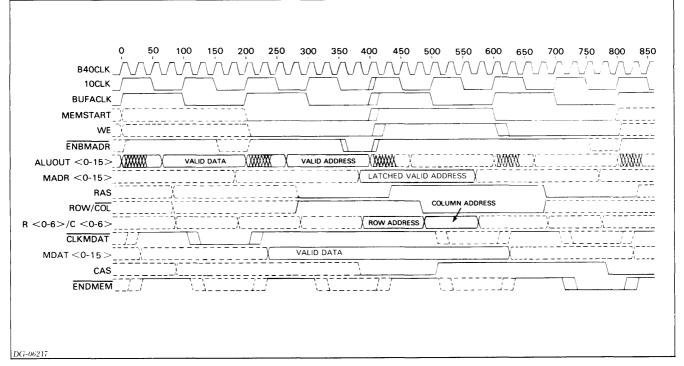

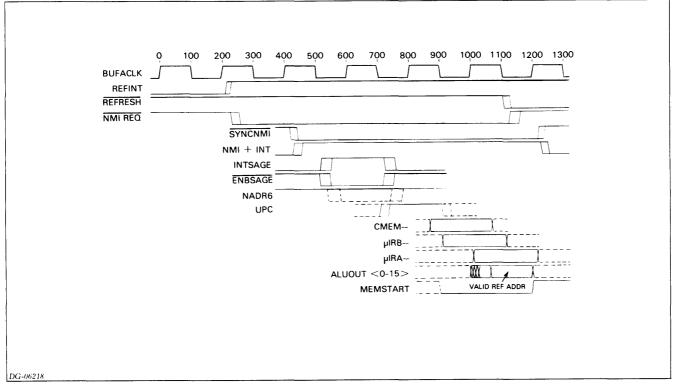

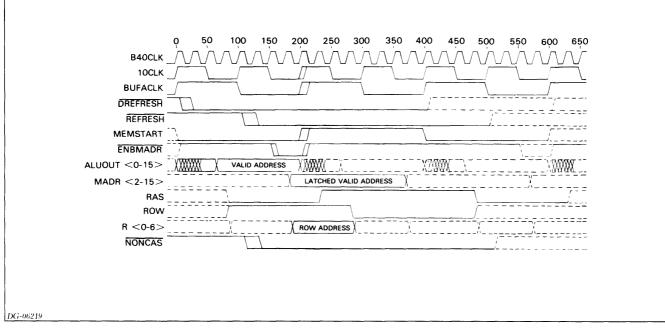

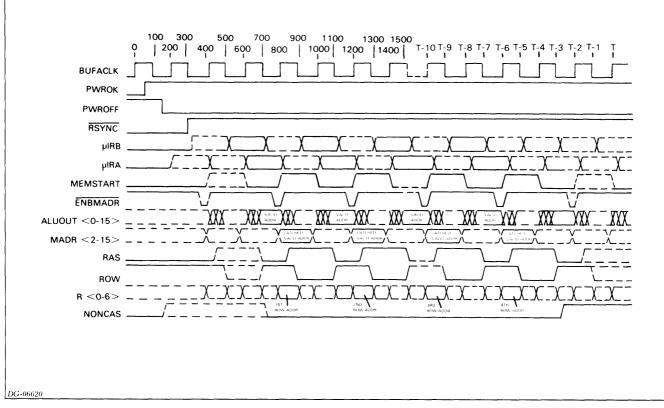

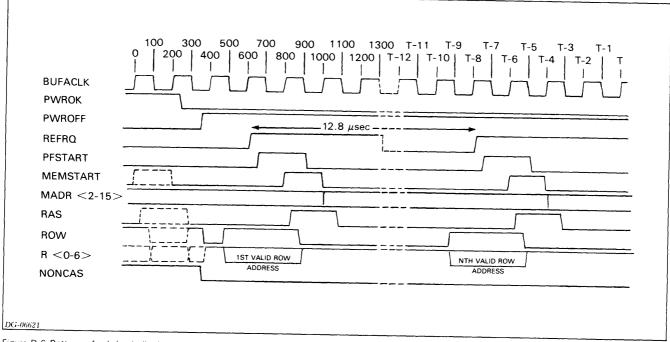

Appendix D MAIN MEMORY TIMING DIAGRAMS

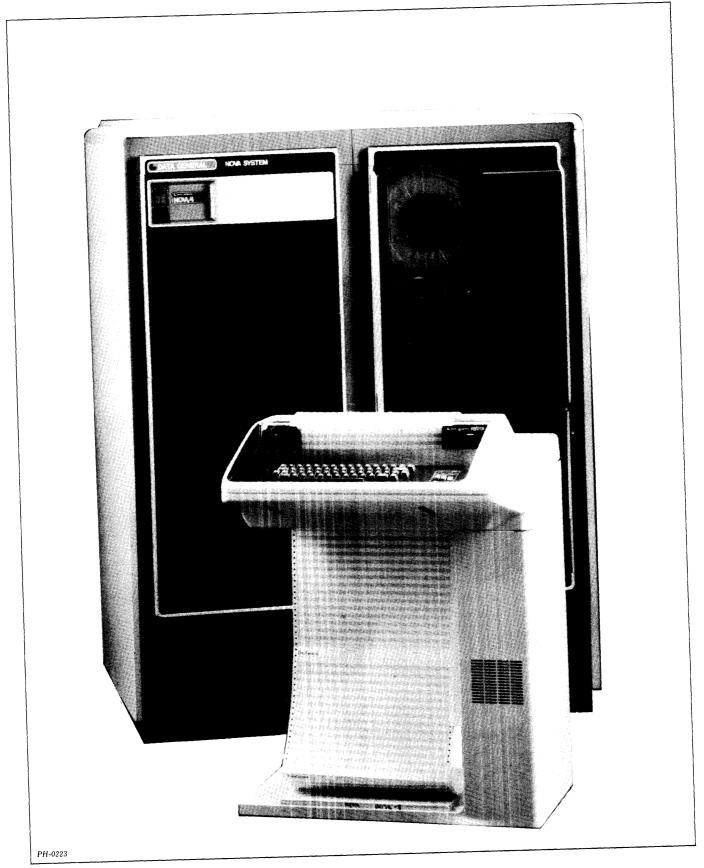

# Part 1 Product Description

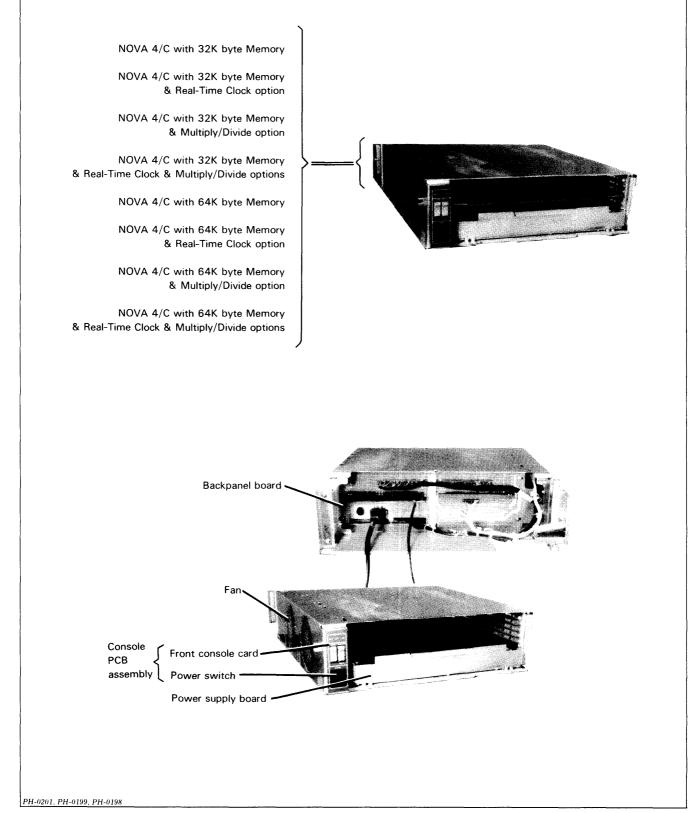

NOVA 4/C computer system

## Chapter 1 INTRODUCTION TO NOVA 4/C COMPUTERS

NOVA 4/C computers incorporate a modular design plus self-diagnostic capabilities that facilitate maintenance and provide high reliability. In most cases, the user can identify the failing field replaceable unit by running simple tests, thus minimizing repair time.

The NOVA 4/C computer supports up to 64K bytes of dynamic RAM (random access memory).

NOVA 4 computers are rack-mounted in NEMA-standard equipment cabinets. These cabinets also provide housing for NOVA line peripheral equipment, such as magnetic tape drives and rack-mounted disc drives.

The computer consists of the following basic modules, which are tailored to the user's selected configuration:

- Computer chassis

- Power supply

- Fan module

- Front console

- Printed circuit CPU board

### CHASSIS

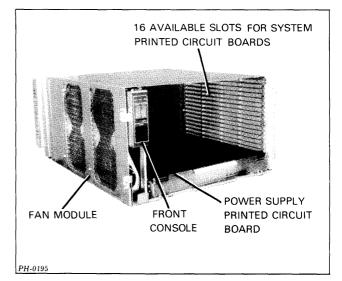

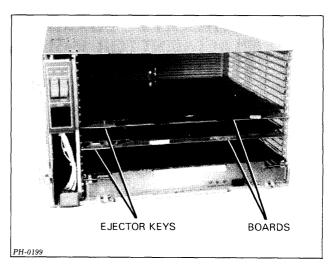

Two computer chassis are available to NOVA 4 users: 5and 16-slot. Each has its own backpanel printed circuit board with connectors for the system printed circuit boards. These boards, including a slide-in power supply board (5 or 16-slot version), are inserted from the front of the chassis, which is easily accessed by removing the NOVA 4 front panel attached to the equipment cabinet. Access to the backpanel is via the rear door of the equipment cabinet.

#### **16-Slot Chassis**

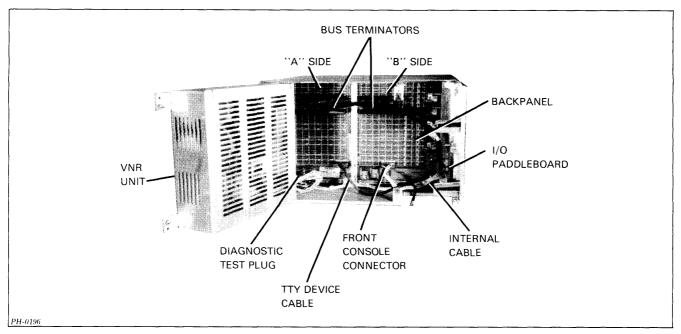

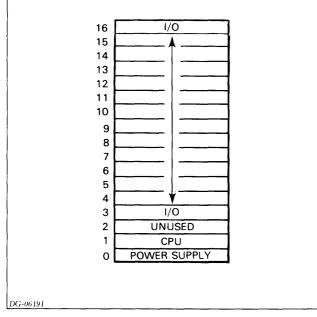

This chassis holds up to sixteen 15-inch by 15-inch printed circuit boards plus the 16-slot power supply and fan module.

Bus termination for the backpanel is provided by a resistor fence (soldered into the backpanel below slot 1) and two bus terminator cards, one for the A side and one for the B side. The bus terminator cards push onto the backpanel pins of slot 2.

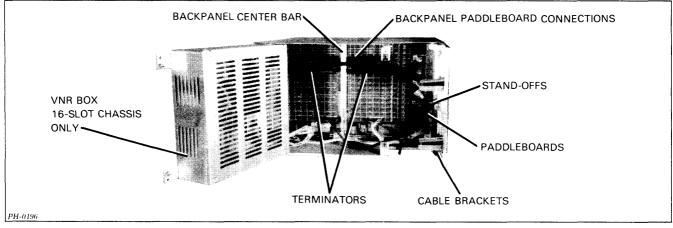

The 16-slot chassis supports up to fifteen I/O paddleboards, which are vertically mounted at the rear of the unit.

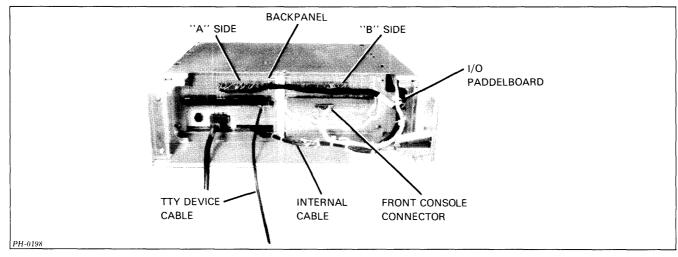

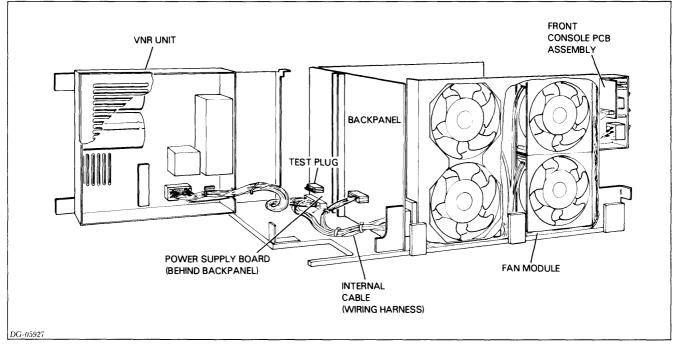

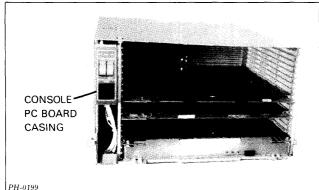

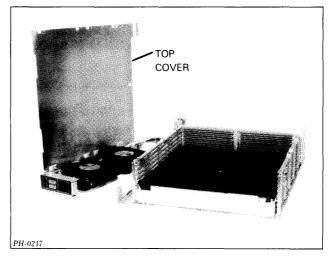

Figure 1.1 16-Slot chassis (front view)

Figure 1.2 16-Slot chassis (rear view)

Figure 1.3 Slot assignment diagram 16-slot chassis

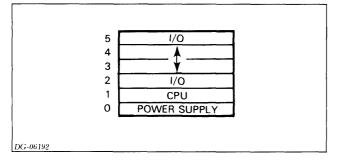

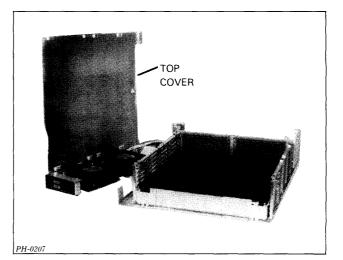

#### **5-Slot Chassis**

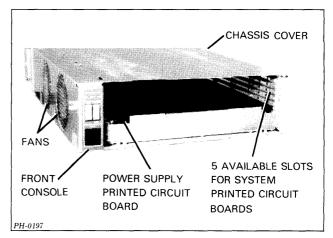

This chassis holds up to five 15-inch by 15-inch printed circuit boards plus the 5-slot power supply and fan modules.

Bus termination for the backpanel is provided by a resistor fence, which is soldered into the backpanel above slot 5.

The 5-slot chassis supports up to four I/O paddleboards. Like the 16-slot chassis, the paddleboards are vertically mounted at the rear of the unit.

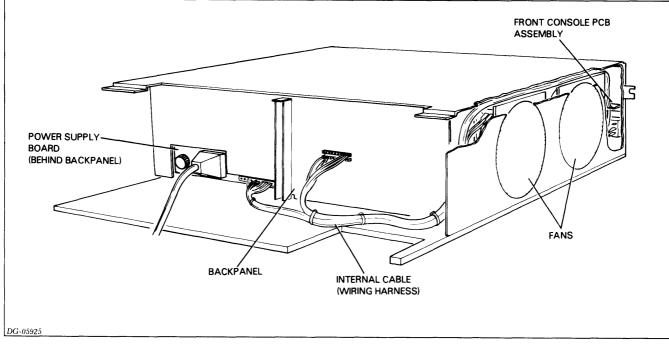

Figure 1.4 5-Slot chassis (front view)

Figure 1.5 5-Slot chassis (rear view)

Figure 1.6 Slot assignment diagram 5-slot chassis

### **POWER SUPPLY**

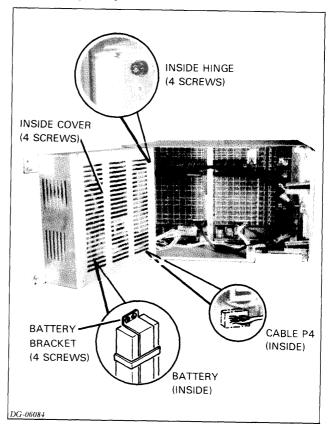

Each chassis has its own power supply, which is available with or without battery backup.

#### **16-Slot Power Supply**

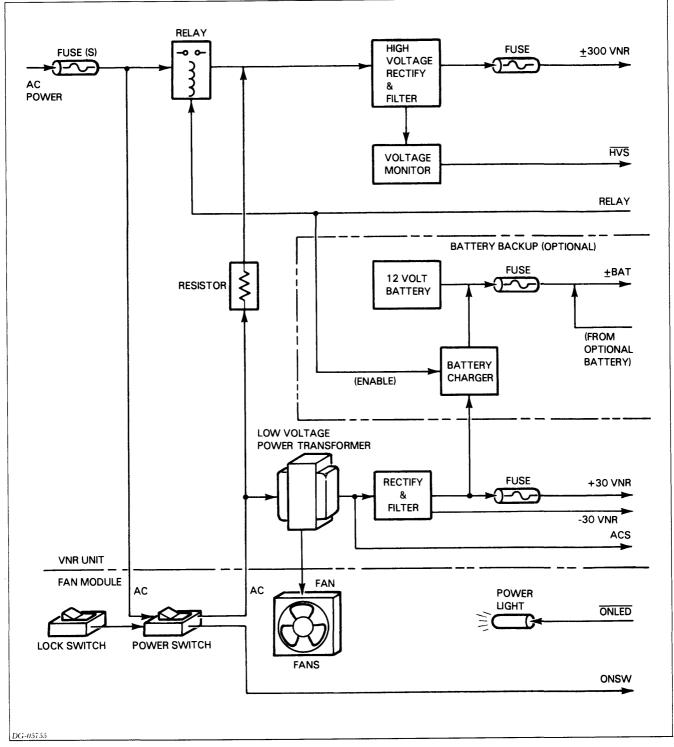

The 16-slot power supply and distribution system consists of a VNR (voltage non-regulated) unit that is vertically mounted to the rear of the chassis and a slide-in power supply printed circuit board which plugs into the chassis backpanel. The VNR unit converts power from the ac supply line to non-regulated dc power, which it furnishes to the power supply board via an internal cable. The internal cable also:

- Carries ac power from the VNR unit to the fan module

- Connects the front console switches and indicators to the backpanel

- · Connects the power switch to the VNR unit.

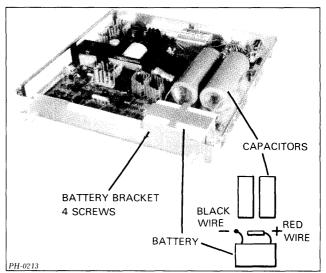

When the battery backup option is present, the VNR unit contains a battery that supplies power to the battery backup circuits in the power supply board.

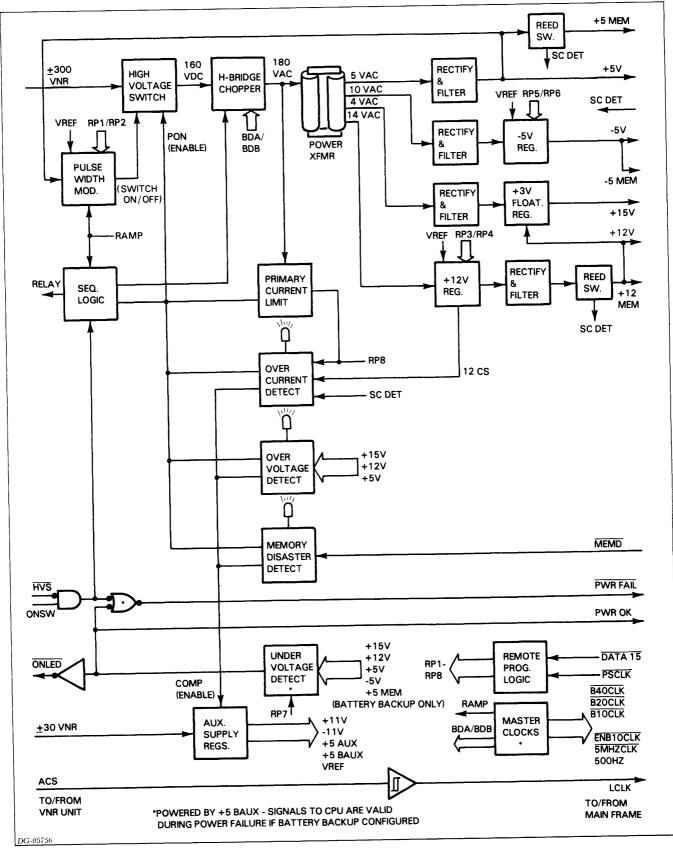

The power supply board regulates the dc voltages from the VNR unit and supplies the required voltages to the remainder of the system via the etch on the backpanel. It also generates the system clocks and supplies them to the system printed circuit boards via the backpanel.

For more information about the operation of the 16-slot power supply, see Part II, Chapter 6, and Part III, Chapter 9.

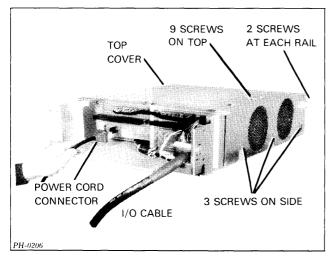

#### **5-Slot Power Supply**

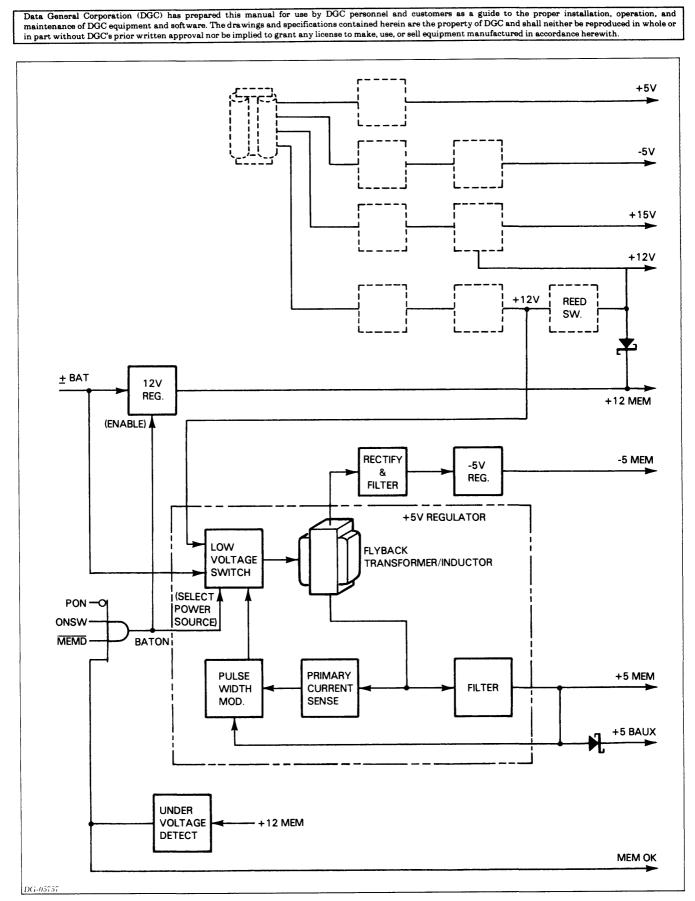

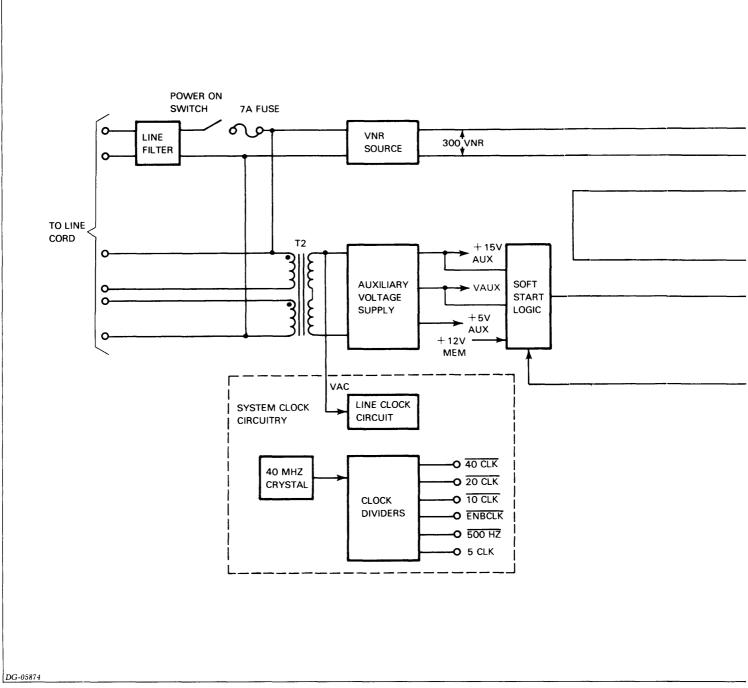

The 5-slot distribution system and power supply resides on a single slide-in power supply printed circuit board. It converts power from the ac supply line to regulated dc voltages. When the battery backup option is present, the battery also resides on the power supply board.

The 5-slot power supply furnishes the required dc voltages to the system printed circuit boards via the etch on the backpanel while it supplies ac power to the fan modules via the internal cable. The internal cable also:

- Connects the front console switches and indicators to the backpanel

- · Connects the power switch to the power supply.

The 5-slot power supply also generates the system clocks and supplies them to the system printed circuit boards via the backpanel.

For more information about the operation of the 5-slot power supply, see Part II, Chapter 6, and Part III, Chapter 10.

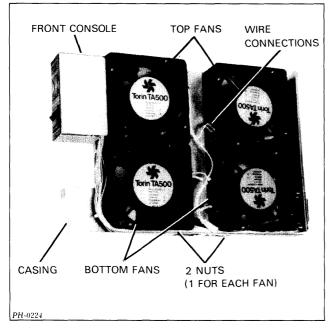

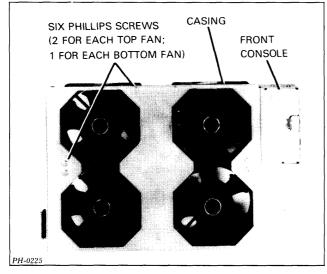

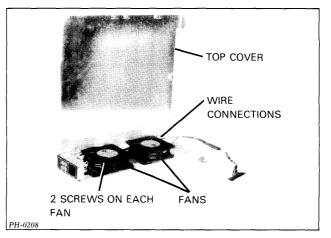

## **FAN MODULES**

Both the 16 and 5-slot fan modules reside on the left side of their respective chassis. They draw air from outside the cabinet and force it through the chassis. On the 16-slot chassis, the fan module, containing four fans, slides into the chassis from the front of the unit. On the 5-slot chassis, two fans mount on the inside of the chassis cover.

## **FRONT CONSOLE**

The front console assembly mounts on the fan module in the 16-slot chassis and on the cover in the 5-slot chassis. It consists of three switches and three indicator lights. The switches allow the user to control basic functions such as power up/down, program load and reset while the indicator lights provide information concerning power status and the CPU's operating mode. The remaining operator control functions are implemented by a virtual console (see below under "CPU Board"). Operator information for both consoles appears in Part I, Chapter 2.

## **CPU BOARD**

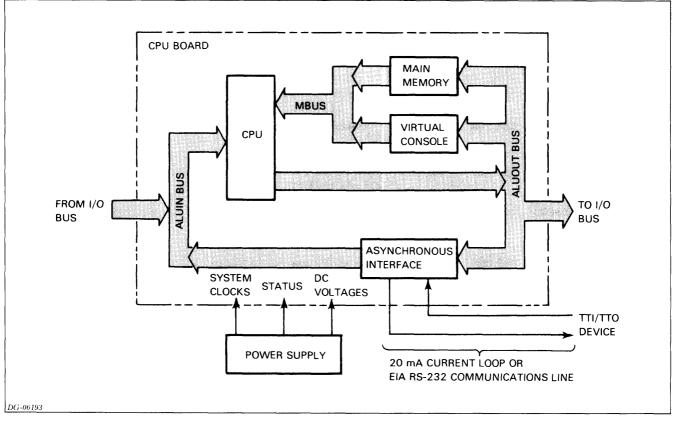

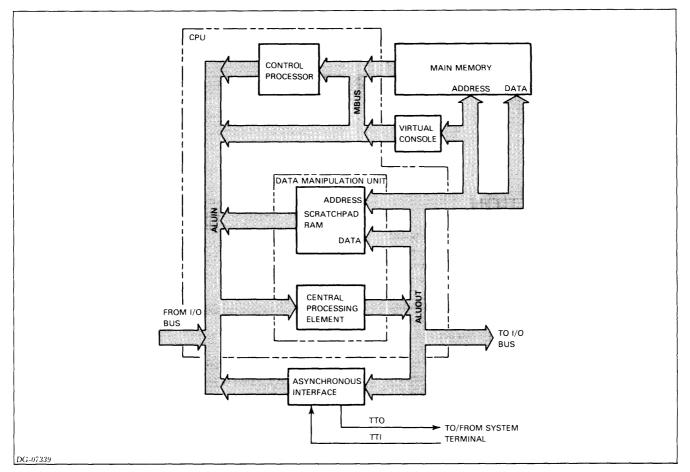

The CPU board occupies slot 1 of the chassis. This board contains:

- Central processing unit (CPU)

- Main memory (dynamic RAM array)

- Full-duplex, asynchronous communications interface

- Virtual console, residing in 512 words of ROM (read only memory) with 16 words of scratchpad RAM

- Programmable real-time clock (optional).

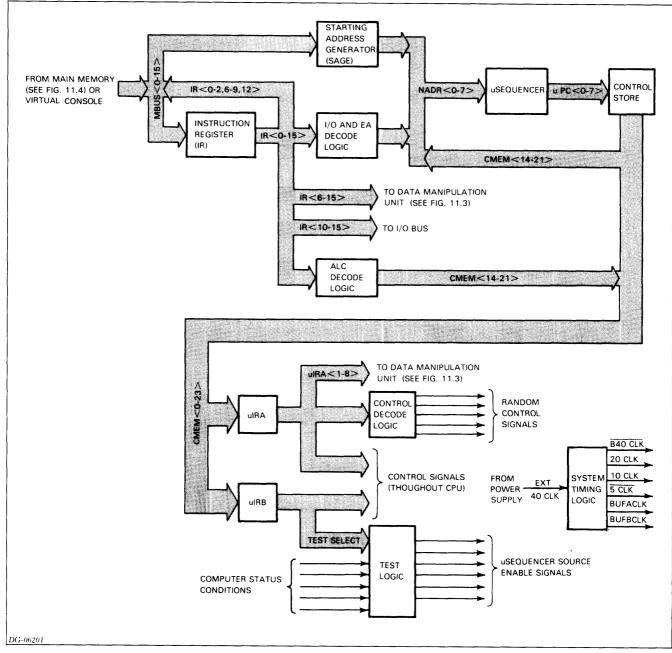

#### CPU

The CPU is a 16-bit microprogrammed processor, which means its data paths are controlled by microinstructions stored in internal ROM. It incorporates the full NOVA 16-bit architecture, including four 16-bit accumulators and hardware stack and frame pointers. NOVA 4 CPUs execute an extended NOVA 3 instruction set, augmented with load and store byte instructions and, optionally, signed multiply and divide instructions.

The CPU operates in two modes: run and console. In run mode, the CPU executes instructions stored in main memory (dynamic RAM). In console mode, the CPU executes instructions stored in the resident virtual console ROM.

On power up or after a power fail when battery backup is not present, the CPU runs a self-test. This test:

- Exercises basic CPU functions

- · Checks main memory

- Checks the operation of the device connected to the resident asynchronous interface.

On completion of the self-test, the CPU enters console mode and is ready to accept user commands. For more information about the self-test, see Part II, Chapter 5.

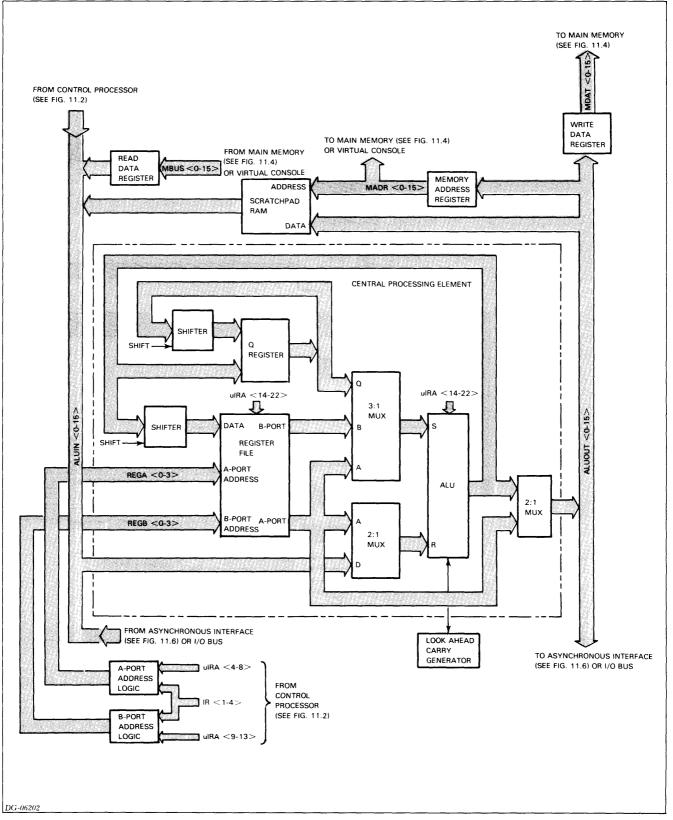

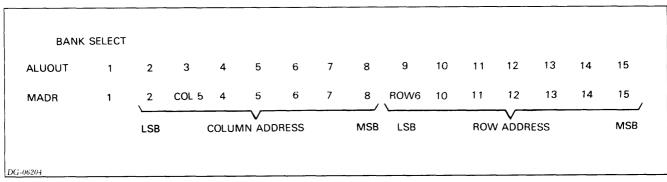

As shown in figure 1.7, the CPU communicates with the main memory and the virtual console via the two internal buses, ALUOUT < 0.15 > and MBUS < 0.15 >. The ALUOUT bus carries 15-bit addresses and 16-bit data words from the CPU to main memory and 9-bit addresses from the CPU to the virtual console. The MBUS bus carries 16-bit data words from main memory and the virtual console to the CPU.

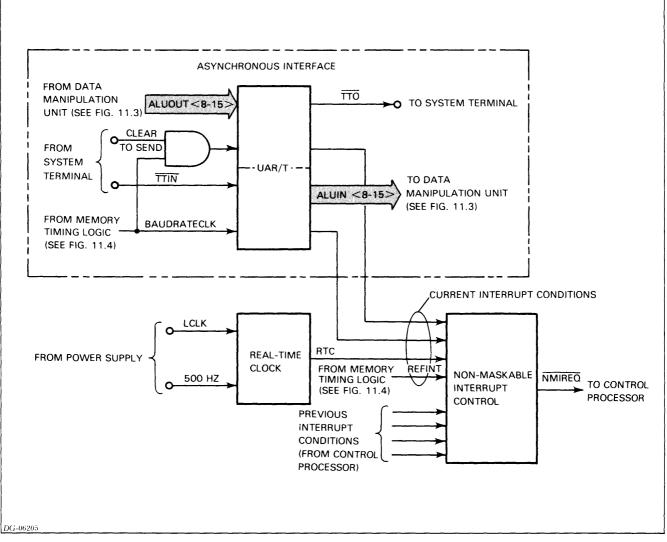

The CPU communicates with the resident asynchronous interface via the two internal buses. ALUOUT<0.15> and ALUIN<0.15>. It communicates with any other I/O controller using the standard 48-line NOVA I/O bus.

Figure 1.7 Simplified printed circuit board interconnection diagram

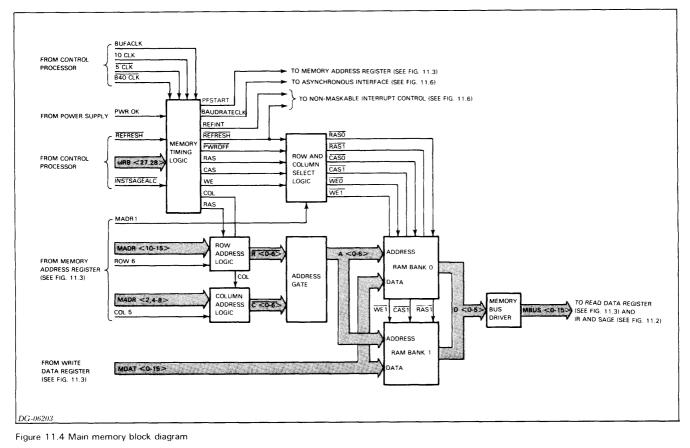

#### Main Memory

Main memory contains a dynamic RAM array and refresh logic. Two different sizes of RAM arrays are available:

- 32K bytes (16K words)

- 64K bytes (32K words)

Each array uses N-channel MOS memory elements which have a 16,384 by 1 bit organization. Memory read/write cycle time is 400 ns.

#### **Asynchronous Interface**

This interface is a programmed I/O controller containing both a transmitter and receiver. It allows full-duplex communications between a serial, asynchronous terminal via either a 20mA current loop or an EIA RS-232C communications line connected to the CPU board's A connector via the backpanel. In addition to standard send/receive terminals, it supports both an automatic send/receive terminal (i.e., a terminal equipped with a paper tape reader) as well as a 60cps DASHER terminal printer.

When the CPU is in run mode and unlocked (as indicated by the position of the front console Lock switch), a BREAK character received by the interface interrupts the executing program and places the CPU in console mode.

#### **Virtual Console**

The virtual console allows a user whose terminal is connected to the resident asynchronous interface to inspect and modify the system's state and aid program debugging.

It provides the user with the ability to:

- Stop, start and continue program execution;

- Examine and/or alter CPU registers and memory locations;

- Initiate program load sequences.

#### **Real-Time Clock**

This optional interface can supply program interrupt requests at one of four program-selectable frequencies: 10Hz, 100Hz, 1000Hz or power line frequency.

For more information concerning the CPU board, see Part III, Chapter 11.

- 11

## FIELD REPLACEABLE UNITS

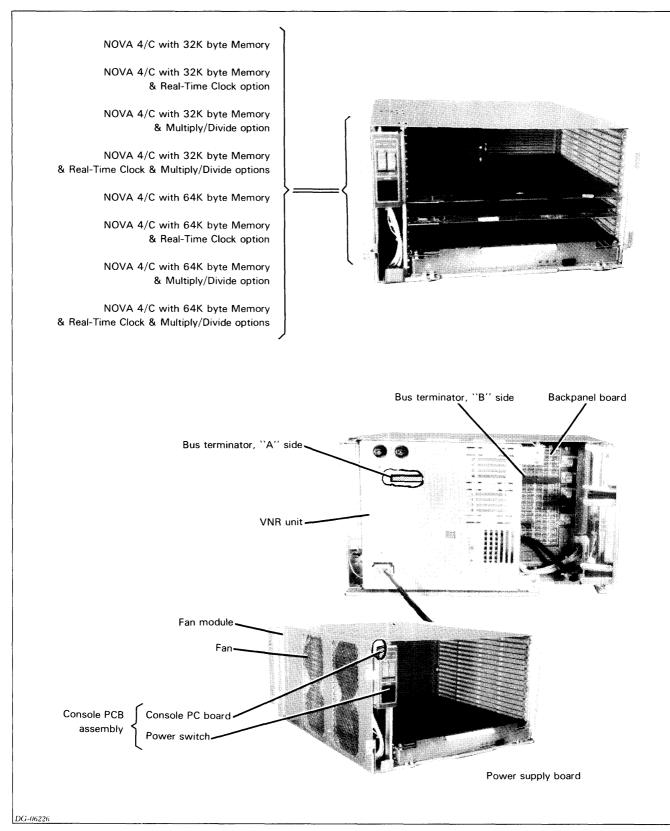

Figures 1.8 and 1.9 show the field replaceable units and their interconnection. Tables 1.1 and 1.2 list their Data General assembly numbers.

| Assem     | Assembly No. ROM Part No. |          | art No.  |                                                                                                       |

|-----------|---------------------------|----------|----------|-------------------------------------------------------------------------------------------------------|

| With ROMs | Without<br>ROMs           | Loc 29N  | Loc 33N  | Description                                                                                           |

| 005-13554 | 005-12413                 | 100-1831 | 100-1832 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory                                                    |

| 005-13553 | 005-12413                 | 100-1833 | 100-1834 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory and real-time<br>clock                             |

| 005-13552 | 005-12413                 | 100-1835 | 100-1836 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory and<br>multiply/divide option                      |

| 005-13551 | 005-12413                 | 100-1837 | 100-1838 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory, real-time<br>clock, and<br>multiply/divide option |

| 005-13550 | 005-12415                 | 100-1831 | 100-1832 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory                                                    |

| 005-13549 | 005-12415                 | 100-1833 | 100-1834 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory and real-time<br>clock                             |

| 005-13548 | 005-12415                 | 100-1835 | 100-1836 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory and<br>multiply/divide option                      |

| 005-13547 | 005-12415                 | 100-1837 | 100-1838 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory, real-time<br>clock, and<br>multiply/divide option |

|           | 005-12073                 |          |          | Backpanel board                                                                                       |

|           | 005-14135                 |          |          | Console PCB assembly                                                                                  |

|           | 005-12429                 |          |          | VNR unit                                                                                              |

|           | 005-12064                 |          |          | Power supply board with battery backup                                                                |

|           | 005-12061                 |          |          | Power supply board<br>without battery<br>backup                                                       |

|           | 115-00163                 |          |          | Fan                                                                                                   |

|           | 005-12076                 |          |          | Fan module                                                                                            |

|           | 005-12438<br>or 005-15361 |          |          | Bus terminator, ``A''<br>side                                                                         |

|           | 005-12439                 |          |          | Bus terminator, ``B''<br>side                                                                         |

|           | 005-12489                 |          |          | Internal cable                                                                                        |

|           | 005-07093                 |          |          | 12V battery                                                                                           |

Table 1.1 16-Slot field replaceable units

Figure 1.8 Exploded view of 16-slot field replaceable units

3

| Assembly No. |                 | ROM Part No. |          |                                                                                                       |

|--------------|-----------------|--------------|----------|-------------------------------------------------------------------------------------------------------|

| With ROMs    | Without<br>ROMs | Loc 29N      | Loc 33N  | Description                                                                                           |

| 005-13554    | 005-12413       | 100-1831     | 100-1832 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory                                                    |

| 005-13553    | 005-12413       | 100-1833     | 100-1834 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory and real-time<br>clock                             |

| 005-13552    | 005-12413       | 100-1835     | 100-1836 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory and<br>multiply/divide option                      |

| 005-13551    | 005-12413       | 100-1837     | 100-1838 | NOVA 4/C CPU with<br>32K byte (16K word)<br>memory, real-time<br>clock, and<br>multiply/divide option |

| 005-13550    | 005-12415       | 100-1831     | 100-1832 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory                                                    |

| 005-13549    | 005-12415       | 100-1833     | 100-1834 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory and real-time<br>clock                             |

| 005-13548    | 005-12415       | 100-1835     | 100-1836 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory and<br>multiply/divide option                      |

| 005-13547    | 005-12415       | 100-1837     | 100-1838 | NOVA 4/C CPU with<br>64K byte (32K word)<br>memory, real-time<br>clock, and<br>multiply/divide option |

|              | 005-12402       |              |          | Backpanel board                                                                                       |

|              | 005-14135       |              |          | Console PCB assembly                                                                                  |

|              | 005-12406       |              |          | Power supply board with battery backup                                                                |

|              | 005-12404       |              |          | Power supply board with battery backup                                                                |

|              | 115-00121       |              |          | Fan                                                                                                   |

|              | 005-13470       |              |          | Internal cable                                                                                        |

|              | 005-12873       |              |          | 6V battery                                                                                            |

Table 1.2 5-Slot field replaceable units

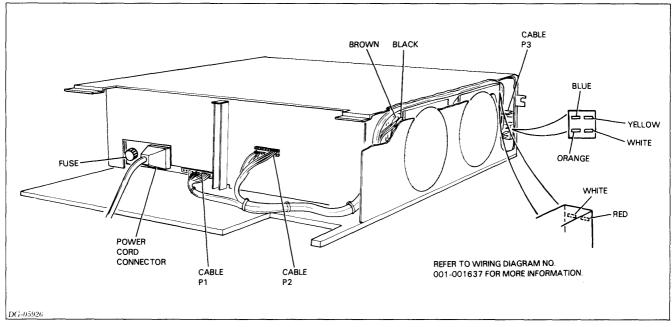

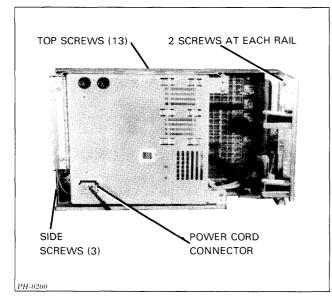

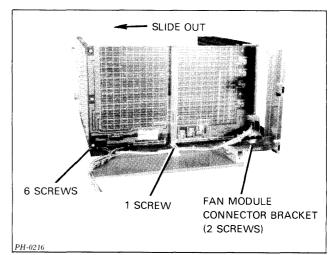

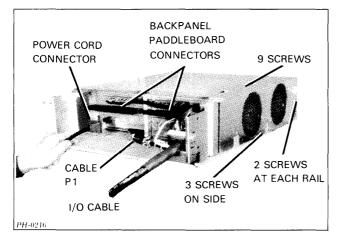

Figure 1.9 Exploded view of 5-slot field replaceable units

1

## **Test Programs**

A list of test programs for the Nova 4/C computers appears in Table 1.3.

| DTOS<br>Mnemonic | Program Description                                                                                                                                                                                                                                                              | Listing No. |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| N3MORT S         | This reliability program consists of<br>a series of individual programs that<br>test the interactive capabilities of<br>the CPU; the CPU-resident<br>real-time clock, asynchronous<br>interface, and memory; and the<br>I/O tester board.                                        | 096-347     |

| N4LGCTST         | This program tests the logic used<br>by the CPU to implement the<br>instruction set. It also performs<br>minimum level testing of the CPU<br>I/O instructions, system terminal<br>I/O, and the program interrupt<br>facility.                                                    | 096-1137    |

| N4EXER           | This program exercises the CPU instruction set and tests the CPU's reliability.                                                                                                                                                                                                  | 096-1136    |

| N4CMD            | This program consists of a series<br>of tests that check main memory<br>for faulty address decoding,<br>memory accessibility, sense<br>amplifier recovery, refresh<br>sensitivity, interaction between<br>memory elements, memory<br>access time and memory cell<br>reliability. | 096-1677    |

| AIODCH F         | This program requires the presence of the multi-mode I/O tester board No. 005-004283. It tests the I/O instructions, the operation of the data channel and the real-time clock.                                                                                                  | 096-1133    |

| RTC TST          | This program tests the operation of the real-time clock.                                                                                                                                                                                                                         | 096-154     |

Table 1.3 Test programs

## **RELATED DOCUMENTATION**

A list of documentation for NOVA 4/C computers appears in Table 1.4.

| Affected<br>Assemblies    | DGC No.    | Description                                                                            |

|---------------------------|------------|----------------------------------------------------------------------------------------|

| NOVA 4/C                  | 014-000617 | NOVA 4 Programmer's<br>Reference Manual                                                |

|                           | 015-000031 | Interface Designer's<br>Reference, NOVA and<br>ECLIPSE Line Computers                  |

|                           | 015-000056 | Diagnostic Operating<br>System Technical Manual                                        |

|                           | 015-000082 | DTOS Summary                                                                           |

| 16-Slot NOVA 4/C          | 010-000213 | Installation Data Sheets,<br>NOVA 4 16-Slot                                            |

|                           | 016-000940 | NOVA 4 16-Slot illustrated parts breakdown                                             |

| 5-Slot NOVA 4/C           | 010-000212 | Installation Data Sheets,<br>NOVA 4 5-Slot                                             |

| CPU Board                 | 001-001600 | CPU schematic                                                                          |

|                           | 016-000857 | CPU with 32K byte memor<br>illustrated parts                                           |

|                           | 016-000864 | CPU with 64K byte memor<br>illustrated parts                                           |

| Power Supply PCB          | 001-001524 | Power Supply schematic                                                                 |

| 16-slot                   | 016-000688 | Power Supply illustrated<br>parts (including battery<br>backup)                        |

| VNR Unit 16-slot          | 001-001523 | Power Supply VNR Card schematic                                                        |

|                           | 016-000670 | Power Supply VNR Card illustrated parts                                                |

| Power Supply PCB          | 001-001616 | Power Supply schematic                                                                 |

| 5-slot                    | 016-000861 | Power Supply illustrated parts                                                         |

| Backpanel 16-slot         | 001-001563 | Backpanel schematic                                                                    |

|                           | 016-000675 | Backpanel illustrated parts                                                            |

| Backpanel 5-slot          | 001-001619 | Backpanel schematic                                                                    |

|                           | 016-000696 | Backpanel illustrated parts                                                            |

| Front Console PCB         | 001-001585 | Front Panel schematic                                                                  |

|                           | 016-000661 | Front Panel illustrated part                                                           |

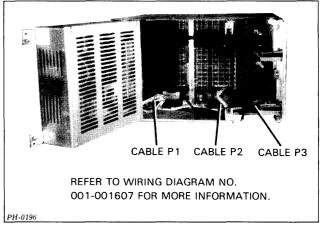

| Internal Cable<br>16-slot | 001-001607 | 16-slot system wiring<br>diagram                                                       |

| Internal Cable 5-slot     | 001-001637 | 5-slot system wiring<br>diagram                                                        |

| I/O Paddleboards          |            |                                                                                        |

| 005-012472                | 008-003294 | Wire list (General Purpose I/O)                                                        |

| 005-012751                | 008-002599 | Wire list (External I/O bus)                                                           |

| 005-012765                | 008-002570 | Wire list (for ULM models<br>4241, 4241A, 4242,<br>4243)                               |

| 005-012476                | 008-003287 | Wire list (Model 8315 Bus<br>Repeater                                                  |

| 005-012590                | 008-003301 | Wire list (DCU 50, models<br>4250, 4254)                                               |

| 005-012473                | 008-003288 | Wire list (asynchronous<br>interfaces, models 4007,<br>4010, 4023, 4075, 4077<br>4078) |

| 005-012585                | 008-003300 | Wire list (MCA, model 420                                                              |

Table 1.4 Documentation summary

## Chapter 2 HOW TO USE THE CONSOLES

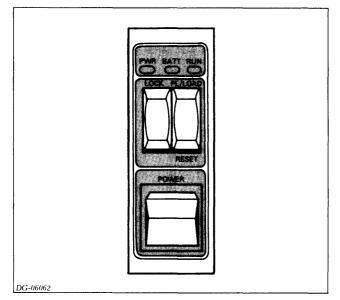

Figure 2.1 Front console

The NOVA 4 computers contain two consoles: a front console and a virtual console. These are described below.

## **FRONT CONSOLE**

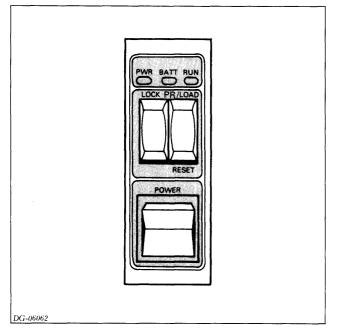

The front console is located on the upper-left corner of the front panel. It consists of the following three switches and three lights.

#### **Switches**

**POWER** - Powers up and powers down the system.

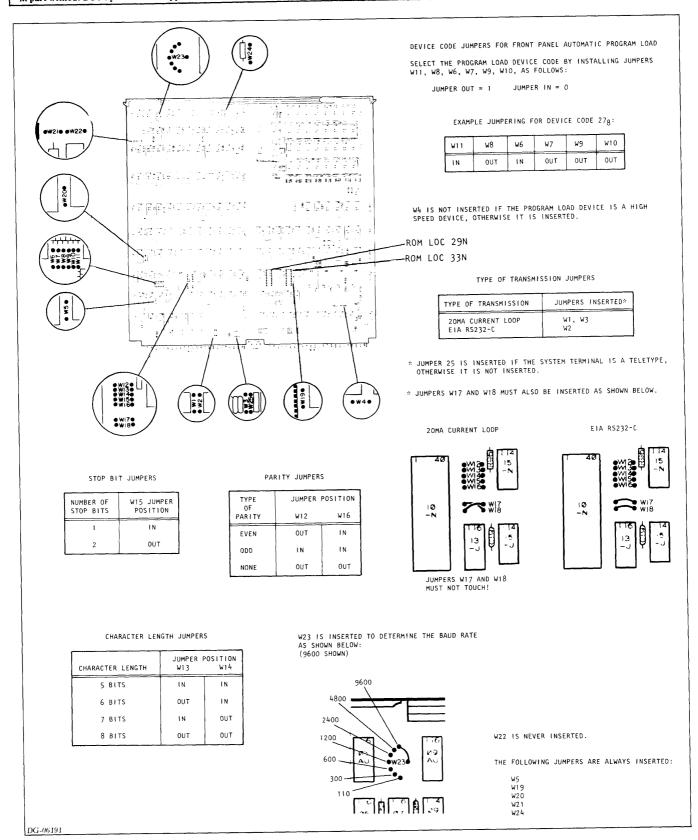

**PL/LOAD-RESET** - When pressed to the PL/LOAD position, the CPU performs a program load from the device whose device code is jumpered on the CPU board. (See installation data sheets or "CPU Board Replacement," Part IV, for jumpering information.)

When pushed to the RESET position, the CPU performs a system reset and enters virtual console mode, described under "Virtual Console."

**LOCK** - When in the LOCK position, the other two switches, described above, are disabled. Additionally, auto restart is

enabled after a power failure when the battery backup is present, while access to the virtual console by a BREAK character from the system terminal is disabled.

In a 16-slot system, if this switch is in the LOCK position, the system cannot be powered down (i.e., the power switch is disabled). In a 5-slot system, if this switch is in the LOCK position and the power switch is placed in the OFF position, the system will go into battery backup mode if that option is present. If the 5-slot system does not contain the battery backup option, the system will be powered down.

#### Lights

**PWR** - When lit, indicates that the system is powered up and the voltages are within operation specifications. When the PL/LOAD-RESET switch is in the RESET position, this light goes out.

**BATT** - When lit, indicates that the system is running on battery backup power. This is usually a result of a power failure.

**RUN-** When lit, indicates that the system is in run mode and/or the PL/LOAD-RESET switch is in the RESET position. This light goes out when the system is in virtual console mode.

## VIRTUAL CONSOLE

The virtual console (VC) allows you to interact with the computer through the system terminal connected to the CPU's on-board asychronous interface. Simple commands which you enter on the terminal's keyboard allow you to: examine and/or modify processor registers or memory locations; start, stop, and continue program execution; and initiate a program load from a selected device.

On power up, the computer performs a self-test. After a successful completion of the self-test, the following information is typed on the terminal:

OK !000000 !

"OK" followed by "!000000" indicates that the self-test ran successfully. The digits following the "!" are the contents

of the program counter, which are all zeroes on power-up. The next "!" is the VC prompt; it tells you that VC is ready and at your service.

In addition to power-up, VC is entered when:

- A HALT instruction is executed,

- The RESET switch on the front console is pressed and the front console is unlocked, or

- The BREAK key on the system terminal is pressed and the front console is unlocked.

Under any of these conditions, the contents of the program counter are typed when the VC is entered. This is followed by the "!" VC prompt. For example, if the program is about to execute an instruction at location 2077 when the VC is entered, the following is typed:

002077

!

### Cells

The VC operates on *cells*. A cell is either a memory location (memory cell) or an internal register (internal cell) such as an accummulator. Each internal register that is accessible by the VC is assigned an internal cell number. The cell numbers are listed in Table 2.1.

| Internal<br>Cell No. | Internal Register                                                                                                                                                                                                                            |  |  |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0-3                  | The contents of the accumulators AC0 through AC3, respectively.                                                                                                                                                                              |  |  |

| 4                    | Return address (the contents of the program counter when the VC was entered).                                                                                                                                                                |  |  |

| 5                    | Stack pointer                                                                                                                                                                                                                                |  |  |

| 6                    | Frame pointer                                                                                                                                                                                                                                |  |  |

| 7                    | Interrupt enable flag status bit:<br>0 = interrupts off<br>1 = interrupts on                                                                                                                                                                 |  |  |

| 11                   | Data switch register: Replaces the conventional console<br>data switches. When the system is in RUN mode (i.e., not<br>in VC mode), and a <i>Reads</i> instruction is executed, the<br>16-bit contents of this register are read by the CPU. |  |  |

| 12                   | Value of the carry bit                                                                                                                                                                                                                       |  |  |

Table 2.1 Internal cells

In order to examine or modify any cell, you must *open* it. Opening a cell causes its contents to be printed, in octal, on the terminal.

## **Cell Commands**

To open a cell, use one of the commands listed in Table 2.2. The VC will respond only to octal numbers and upper case letters. In the table, *current cell* means the last cell that you opened.

| Command                    | Function                                                                                                                             |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|

| nA                         | Open the internal cell whose internal cell number is equal to $n.$ (See Table 2.1.)                                                  |  |  |

| n/                         | Open the memory location whose address is equal to the octal number $n$ .                                                            |  |  |

| (carriage<br>return)       | Close the current cell and open the next consecutive cell.                                                                           |  |  |

| (line feed<br>or new line) | Close the current cell but do not open another.                                                                                      |  |  |

| /                          | Close the current cell and open the memory cell whose<br>address is equal to the contents of the current memory or<br>internal cell. |  |  |

Table 2.2 Cell commands

When you open a memory cell, the VC interprets the address as a 15-bit physical address. You do not have to type leading zeroes. All you have to type is the physical address in octal representation. For example, if you want to open location 5, type 5/. If you want to examine the top location of a system which contains 64K bytes of memory, type 77777/.

Once you have opened a cell, you may change its contents by simply typing the octal number whose value is to be placed in the cell. Terminate the expression with a Carriage Return, Line Feed, or New Line. Note that if you type Carriage Return, the next cell will also be opened. This is convenient when you need to enter data into several consecutive locations. If you type **R** or **L** immediately after opening a cell, the contents of the cell are used as the value of *n* for the **R** or **L** command.

### **Function Commands**

Table 2.3 lists the VC function commands. All commands must be typed in octal numbers and upper case letters.

| Command | Function                                                                                                                                                      |  |  |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Р       | Starts program execution at the memory location specified by the contents of internal cell number 4. (See Table 2.1.)                                         |  |  |

| nR      | Issues an I/O Reset and starts program execution at the memory location specified by the octal number $n.$                                                    |  |  |

| 1       | Issues an I/O Reset.                                                                                                                                          |  |  |

| nL      | Performs a program load from the device whose device<br>code is equal to $n$ . Bit 0 of $n$ is a 0 for a low-speed device<br>and a 1 for a high-speed device. |  |  |

| F       | Performs a DG field service cassette bootstrap load. (For DGC use only.)                                                                                      |  |  |

| К       | Cancels the entire line just typed, and prints a question mark (?).                                                                                           |  |  |

Table 2.3 Function commands

The VC has two commands to start program execution. Typing **P** starts program execution at the location specified by internal cell number 4 (the return address). You can also start program execution by typing  $n\mathbf{R}$ . In this case, the CPU issues an I/O Reset command and starts program execution at the location specified by the octal number n.

Typing I causes the CPU to issue an I/O Reset command.

You can program load from an I/O device by typing nL where n is the device code, in octal, of the I/O device to be used. Bit 0 of n should be 1 if the I/O device is high-speed, and 0 if the I/O device is low-speed. For example, if the program load device is a high-speed 6060 disc drive whose device code is 27, you would type the following:

100027L

You can perform a Data General field service cassette bootstrap by typing F.

#### **Virtual Console Errors**

If you type a character that the VC does not recognize, it will print a ? followed by a New Line. If you wish to cancel an entire line you have just entered, type a **K**. In this case, VC will respond with a ? followed by a New Line.

If you attempt to open a non-existent memory cell, the 16-bit contents of the cell printed on the terminal are meaningless. If you attempt to open an internal cell with a cell number greater than 13, VC will respond with a **?**.

## Part 2 Troubleshooting

**Data General Corporation**

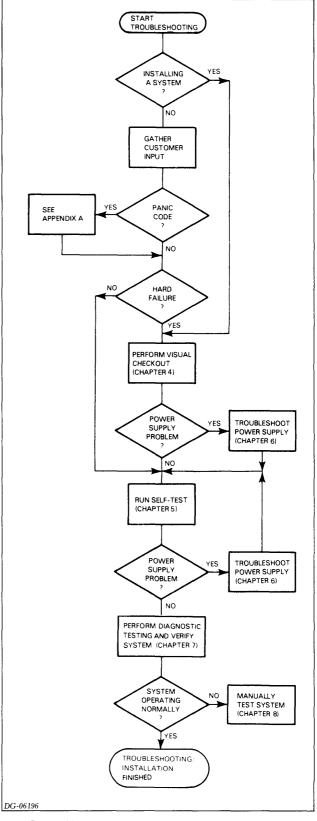

## Chapter 3 INTRODUCTION TO TROUBLESHOOTING

Part 2 of this manual contains troubleshooting procedures intended for use during:

- Initial checkout of a new installation or addition to an existing system;

- Repair of an existing system.

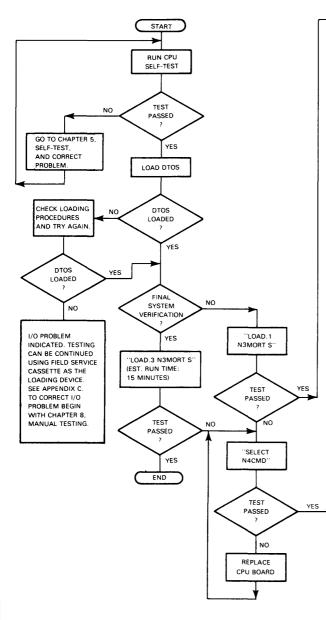

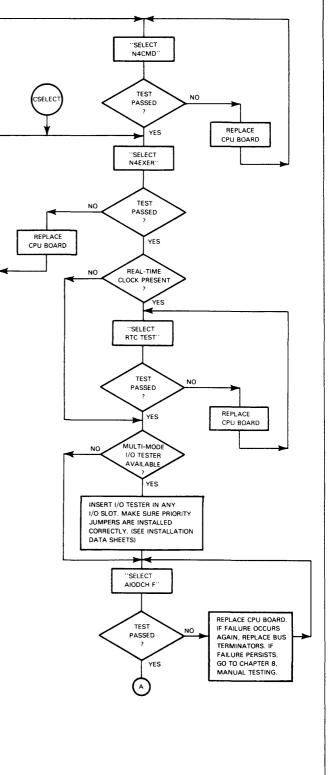

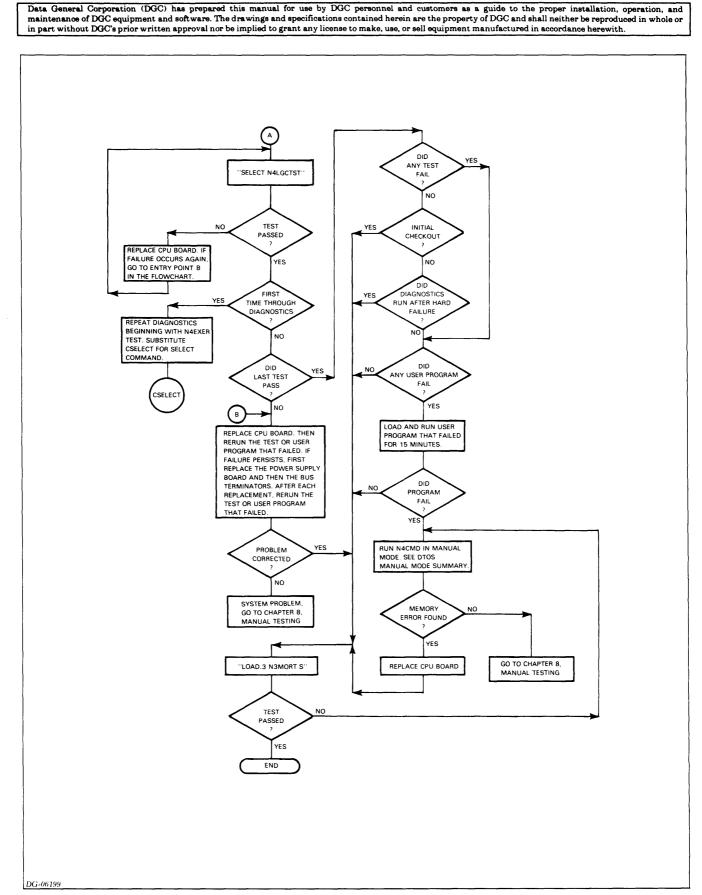

While these situations are different, many of the procedures required to perform both initial checkout and repair are the same, as shown in the Troubleshooting Flowchart, Figure 3.1. This flowchart leads you through a logical sequence of fault isolation, referencing Chapters 4 through 8. These chapters contain step-by-step procedures for detecting faulty assemblies and checking the reliability of the system. (Actual replacement procedures are outlined in Part 4.)

## **PRE-SITE INFORMATION**

Before going to the customer's site, check the list below and learn the customer's configuration, if possible. This will help to ensure that you have the appropriate field replaceable units (FRUs) with you on arrival.

- Chassis: 16 or 5-slot

- Main memory size

- CPU options

- Battery backup option

- Terminal used as system console

- Other peripherals

Also if you are going to repair a failing unit, try to get information from the customer that may give you a clue to the failing FRU.

## **CONFIGURATION CHART**

Each system is shipped with a configuration chart which should reflect its configuration. Attach the chart to the rear door (outside) of the cabinet. Whenever you or anyone else reconfigures or retailors the system, update the chart to reflect the changes.

## **INITIAL CHECKOUT**

If you are performing an initial checkout of a new installation, start with Chapter 4 and follow the steps outlined in the troubleshooting flowchart.

#### REPAIR

If you are servicing a failing system, the type of failure determines the procedures you will use to troubleshoot it. Thus, it is important to ask the customer the following questions:

- 1. Was the computer operating properly before the failure?

- 2. Is the failure a hard or intermittent one?

- 3. Did the operating system generate any panic codes?

- 4. Can the computer successfully complete the self-test?

- 5. Was the failure detected by reliability and/or diagnostic testing?

6. Was the failure detected while running user programs? With the answers to these questions, you are now ready to follow the steps indicated in the Troubleshooting Flowchart (Figure 3.1).

Figure 3.1 Troubleshooting flowchart

## Chapter 4 VISUAL CHECKOUT

You should perform the visual checkout whenever you initially check out a system (or addition to a system) or repair an existing system.

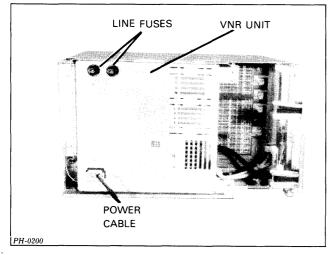

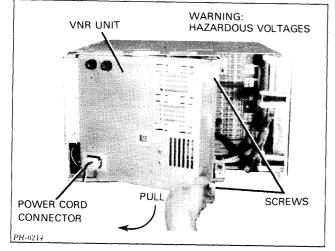

Warning: The VNR unit (16-slot only) and the slide-in power supply board (both chassis) carry dangerously high voltages. Turn the power off before removing any unit.

Visually checkout the system using the following procedure. Try to correct any simple problems you find.

1. Turn power off.

**2.** Check the configuration chart on the rear door (outside) of the cabinet to find out what the system contains and how it is tailored.

**3.** Open the rear cabinet door and unplug the ac line cord from the cabinet.

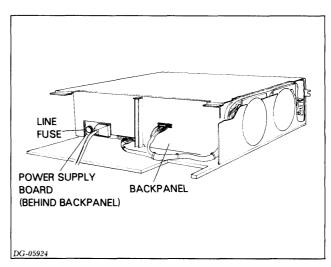

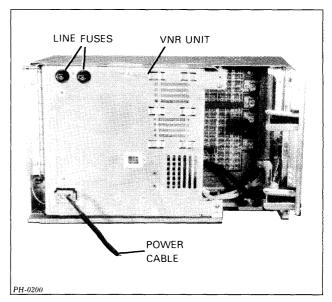

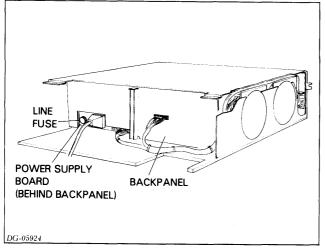

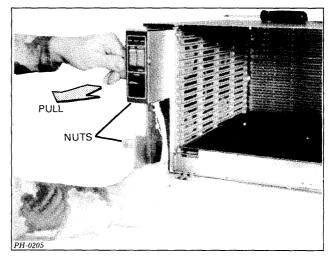

**4.** If you are repairing a system, check the ac line fuses and replace them if they are blown. The 16-slot power supply has two 15 Amp line fuses which screw into the rear of the VNR unit (see Figure 4.1). The 5-slot power supply has one 7 AMP line fuse which screws into the rear of the power supply board and extends through a cutout in the backpanel (see Figure 4.2).

Figure 4.1 Line fuses for 16-slot power supply

Figure 4.2 Line fuse for 5-slot power supply

5. On a 16-slot chassis:

**a.** Swing the VNR unit away from the backpanel (see "VNR Unit Replacement," Part 4).

**b.** Check for bent pins which cause shorts. Straighten any bent pins.

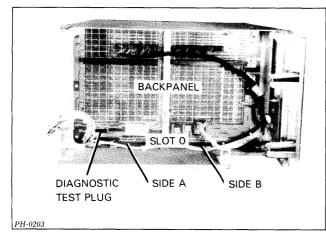

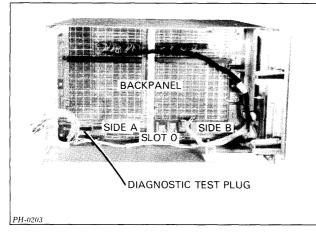

**c.** Make sure the diagnostic test plug is inserted with the RUN label up (see Figure 4.3). If it is not, remove the plug, turn it over, and reinsert it with the RUN side up.

**d.** Make sure none of the connectors to the backpanel or to the paddleboards are hanging loose.

**e.** If you are repairing a system which you suspect has had an I/O problem since installation:

- Make sure the priority jumpers are inserted as described in the installation data sheets.

- Make sure the correct paddleboards are used and connected to the proper backpanel slots (see installation data sheets).

f. Reposition the VNR unit (see "VNR Unit Replacement", Part 4).

6. On a 5-slot chassis:

**a.** Check for bent pins which cause shorts. Straighten any bent pins.

**b.** Make sure none of the connectors to the backpanel or to the paddleboards are hanging loose.

Figure 4.3 Diagnostic test plug

**c.** If you are repairing a system which you suspect has had an I/O problem since installation:

- Make sure the priority jumpers are inserted as described in the installation data sheets.

- Make sure the correct paddleboards are used and connected to the proper backpanel slots (see installation data sheets).

7. Plug the ac line cord back into the cabinet and close the rear cabinet door.

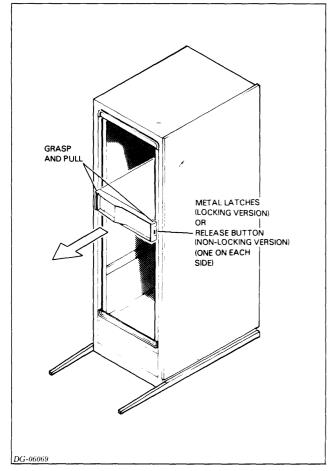

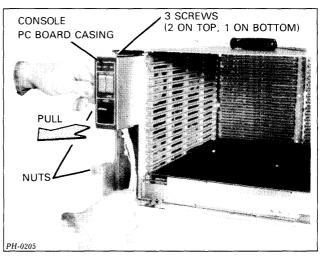

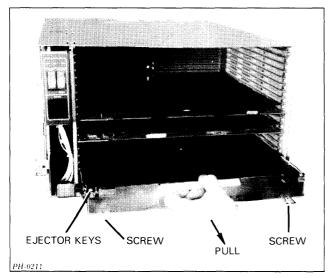

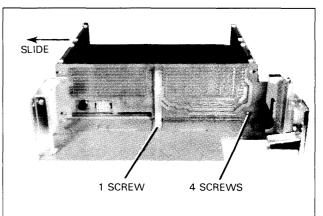

8. Remove the front panel (see "Front Panel Replacement," Part 4).

**9.** If you are installing a system or repairing a system which has never operated normally:

**a.** Remove each printed circuit board one board at a time, except the power supply board, and make sure it is tailored properly (see "CPU Board Replacement," Part 4, or the appropriate I/O device documentation). Replace the board before removing the next.

**b.** If necessary, update the configuration chart on the rear (outside) of the cabinet door to reflect the proper tailoring.

**10.** Check the fans as follows:

**a.** If you are servicing a 16-slot chassis with boards in slots 6 and 15, remove them. If you are servicing a 5-slot chassis with a board in slot 4, remove it.

**b.** Turn the power on.

**c.** Look through the open slots on the left side of the chassis and see if all the fans are running. You may need to use a flashlight. If all the fans are running, continue the visual checkout; otherwise, proceed as follows:

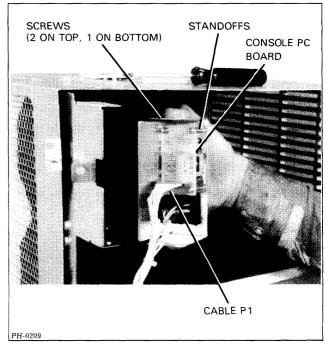

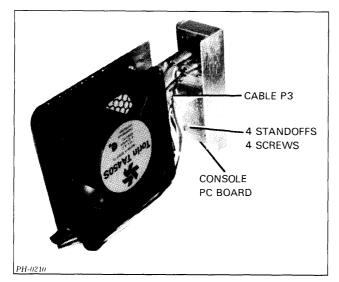

- If some, but not all, of the fans are running, replace the faulty fans and make sure the cable connectors to the fans and the console PCB assembly are seated securely.

- If none of the fans are running, go to Chapter 6, Troubleshooting the Power Supplies.

- After correcting the problem, continue the visual checkout.

- **d.** Turn the power off and reinsert any boards you removed.

**11.** Replace the front panel (see "Front Panel Replacement," Part 4).

**12.** Turn the power on and check the Power-On light on the front console. If the power light is on, you can assume that the voltages are within operating margins. In this case, go to Chapter 5, *Computer Self-Test*; otherwise, go to Chapter 6, *Troubleshooting the Power Supplies*. After correcting the power supply problem, go to Chapter 5.

## Chapter 5 COMPUTER SELF-TEST

Whenever the computer is powered up with the Lock switch off, the CPU automatically runs a 4-second self-test to ensure that the computer can load and run diagnostic programs. (The CPU also runs this test after a power failure when battery backup is not present.) The self-test consists of several ROM-resident diagnostic tests which check the operation of the power supply, the system terminal, the basic CPU functions, and main memory. As the CPU completes portions of the self-test it prints (displays) part of the following message on the system terminal:

OK !000000 '

The last exclamation point (!) is the VC prompt.

If the entire message is printed, all the diagnostic tests have run and the self-test is successfully completed. If only part of the message is printed, the self-test found a bad unit. The indicator lights on the front console together with the printed part of the message indicates the probable faulty unit as shown in the Table 5.1.

| Power light | Run light | Messgae<br>printed on<br>system<br>console | Fault indicated                |

|-------------|-----------|--------------------------------------------|--------------------------------|

| Off         | On or Off |                                            | Power supply                   |

| On          | Off       |                                            | CPU/System terminal            |

| On          | Off       | 0                                          | Main memory<br>(first 32KB) *  |

| On          | Off       | ОК                                         | Main memory<br>(second 32KB) * |

Table 5.1 Fault indicators

\*In a 32K byte (16 Kword) system, this fault indicates a fault somewhere in the entire 32K byte memory.

### TROUBLESHOOTING WITH THE SELF-TEST

Check out the computer with the self-test as follows:

1. Switch the power on.

**2.** If the self-test is completed (the entire message is printed out) and any problems found during the visual check are corrected, go to Chapter 7, *Diagnostic Testing*.

**3.** If the self-test is not successfully completed, follow the procedure given below for the fault indicated. Turn off the power before removing or installing any board. If you replace a board and the self-test still indicates the same fault, replace the original board before continuing, unless otherwise indicated. Procedures for replacing FRUs are given in Part 4.

**NOTE:** Each time you replace a FRU, repeat steps 1 through 3 until the self-test is successfully completed.

#### **Power Supply Fault**

Go to Chapter 6, Troubleshooting the Power Supplies.

### **CPU/System Terminal Fault**

**1.** Visually check out the terminal as follows:

**a.** Make sure the connectors on the device cable for the system terminal are securely plugged into the backpanel and the terminal.

**b.** Make sure that the terminal is connected to the ac line source, turned on, on-line, and in upper case mode. Also make sure that the correct interface type and baud rate are selected (see *CPU Board Replacement*, Part 4).

**2.** If you have any reason to think that the terminal is faulty, go to step 4a; otherwise, continue to step 3.

3. Check for a faulty CPU as follows:

a. Replace the CPU board.

**b.** If the self-test still indicates a CPU/system terminal fault, do the following:

- Enter the virtual console (VC) by pressing the RESET switch on the front console.

- Read the contents of accumulators AC0, AC1, and AC2 using the VC (see Chapter 2).

- Replace the new CPU board with the original CPU board and repeat two previous steps.

- If the contents of the accumulators are NOT identical in both cases, both CPU boards are probably faulty. Try another CPU board, if you have one.

- If the contents of the accumulators are identical in both cases, remove all the printed circuit boards from the chassis except the power supply board and the CPU board. If the self-test still indicates a CPU/system terminal fault, replace the power supply board.

**4.** If the self-test still indicates a CPU/system terminal fault, check out the system terminal as follows:

**a.** If you have NOT already replaced the CPU board, replace the CPU board. If the self-test still indicates a CPU/system terminal fault with the new CPU board, check the contents of the accumulators as described in step 3b, using both the new and original CPU boards. If the contents of the accumulators are identical for both boards, continue to step b below; otherwise, try another CPU board, if you have one.

**b.** See if the system terminal works in local mode. If it does, replace the device cable; otherwise, troubleshoot the system terminal (see the documentation for the appropriate terminal).

**c.** If the terminal uses an EIA interface and you have NOT already replaced the power supply board, replace the power supply board.

**5.** If you have already replaced the CPU and power supply boards in a 16-slot chassis, replace the bus terminators.

### Main Memory Fault (First or Second 32KB)

1. Replace the CPU board.

2. If the self-test still indicates a memory fault with the new CPU board, check the contents of the accumulators as described in "CPU Fault," step 3b, using both the new and original CPU boards. If the contents of the accumulators are identical for both boards, replace the power supply board; otherwise, try another CPU board, if you have one.

## Chapter 6 TROUBLESHOOTING THE POWER SUPPLIES

Figure 6.1 Front console indicator lights

This chapter will help you find the failing field replaceable units in the power supply and power distribution system. When you find a failing unit, replace it following the replacement procedure given in Part 4. For a detailed description of how the power supply operates, see Chapters 9 or 10.

### **OVERVIEW**

Before you try to troubleshoot the power supply, it is helpful to know what the power supply does and how its indicator lights function.

#### **Major Functions**

The power supplies for both the 16-slot and the 5-slot chassis perform the following functions:

- Supply regulated dc operating voltages for the chassis

- Supply ac voltages for the fans

- Generate a time base for the CPU and real-time clock

- Detect and respond to emergency conditions (power loss, excessive voltage or current, etc.)

- Provide power status indicators for the CPU (power fail, power ok, etc.)

- Provide emergency battery backup for the memory voltages (optional).

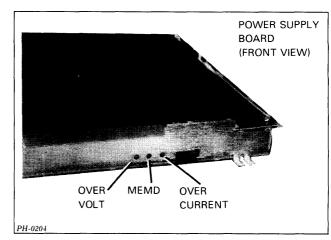

Figure 6.2 Power supply board indicator lights

### **Indicator Lights**

Two indicator lights on the front console of both chassis display the status of the power supply (see Figure 6.1).

**POWER-ON LIGHT** - Indicates that the dc voltages are stable. If the power switch is on and the light is out, one of the following may have occurred:

- Ac power brownout or blackout

- Power supply failure

- Excessive load or short circuit on backpanel

- Diagnostic test plug not in "RUN" position (16-slot chassis only).

**BATTERY BACKUP LIGHT** - Indicates that the battery is supplying the dc operating votages for the memories because either a power line failure, a power supply failure, or a shutdown (due to external shorts) occurred.

The 16-slot chassis has three additional indicator lights which give further status information. These lights are located on the front of the power supply board as shown in Figure 6.2.

Figure 6.3 16-Slot power supply

**OVER-CURRENT LIGHT** - Indicates that an over-current condition appeared in the supply or on the backpanel. The supply automatically tries to recover from an over-current condition. As a result, you may see this light blink up to 6 times before it finally stays on. Once it stays on you must power the supply down to clear the fault light (this probably will not correct the fault).

**OVER-VOLTAGE LIGHT** - Indicates that an over-voltage condition appeared in the supply. You must power the supply down to clear the fault light (this probably will not correct the fault).

**MEMORY DISASTER LIGHT** - Indicates that the main memory detected a dc power failure on -5 MEM. You must power the supply down to clear the fault light (this probably will not correct the fault).

#### **Functional Description**

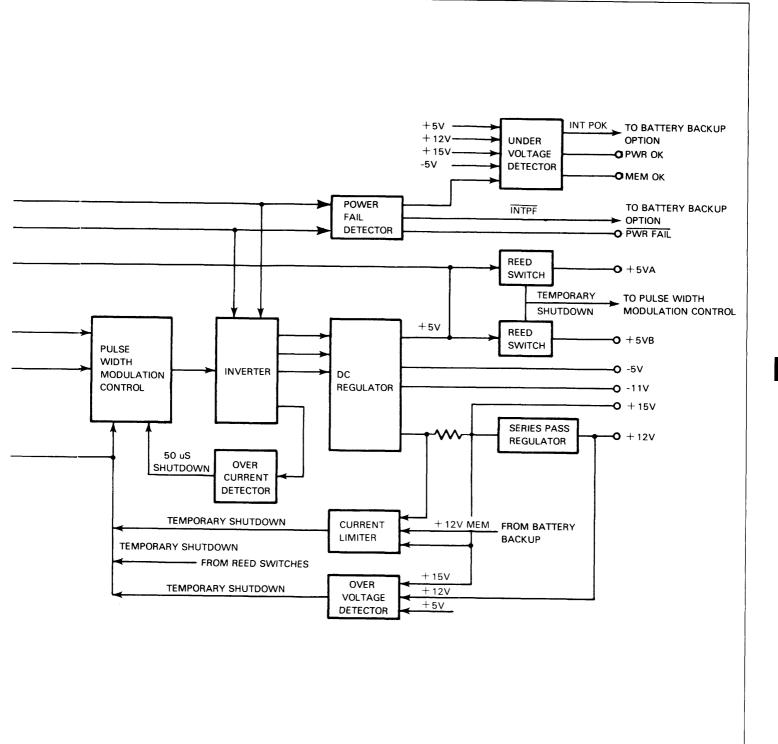

#### **16-Slot Power Supply**

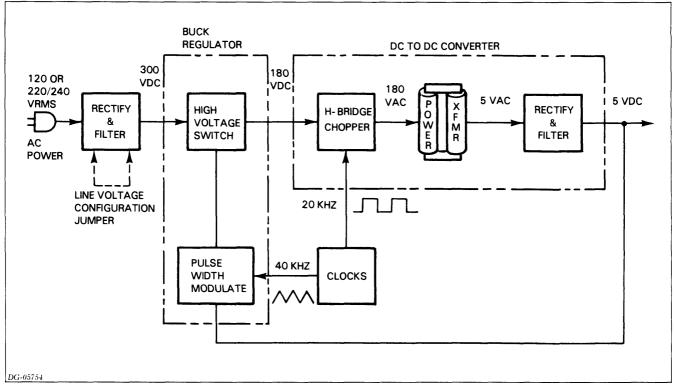

The power supply and distribution system for the 16-slot chassis consists of a VNR unit, a power supply printed circuit board, a fan module, a front console PCB assembly, and a backpanel circuit board. These modules are interconnected by an internal cable (wiring harness) and by etch on the backpanel, as shown in Figure 6.3.

The VNR unit converts power from the ac line to unregulated dc voltages for the power supply board. It also routes ac power to the fans in the fan module. In a system with battery backup, the VNR unit contains a battery charger along with a small battery that supplies power for the battery backup circuits on the power supply board. A plug on the back of the unit lets you connect an external battery when longer backup times are required. The power supply board is a printed circuit board which regulates the dc voltages from the VNR unit and in turn powers the chassis. It also provides clock and status signals for the CPU board. Fault detection circuits automatically shut down the power supply if an emergency condition occurs.

The backpanel routes power, control, and status signals between the power supply board and the printed circuit boards. It includes several reed switches that detect excessive current flow in the printed circuit boards. (These switches replace the fuses commonly found on other backpanels.)

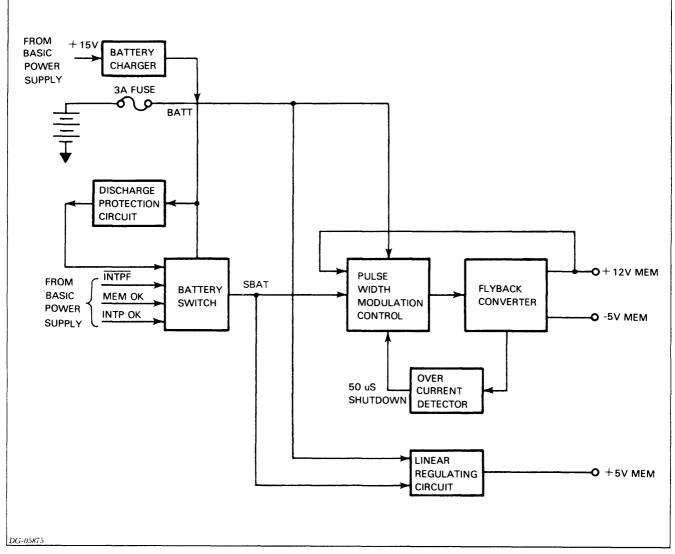

#### **5-Slot Power Supply**

The power supply and distribution system for the 5-slot chassis consist of a power supply board, a fan module, a console PCB assembly, and a backpanel circuit board. These modules are interconnected by an internal cable (wiring harness) and by etch on the backpanel, as shown in Figure 6.4.

The power supply board converts the power from the ac line to regulated dc voltages and in turn powers the chassis. It also provides clock and status signals for the CPU and main memory. Fault detection circuits automatically shut down the supply if an emergency condition occurs. In a system with battery backup, the power supply board contains a battery charger along with a small battery that supplies power for the battery backup circuits.

The backpanel routes power, control, and status signals between the power supply circuit board and the printed circuit boards.

Figure 6.4 5-Slot power supply

### TROUBLESHOOTING 16-SLOT POWER SUPPLY

WARNING: The VNR unit and power supply board generate dangerously high voltages. DO NOT ATTEMPT TO MEASURE VOLTAGES INSIDE THEM. Before you remove the cover on the VNR unit or the power supply board, WAIT AT LEAST 5 MINUTES AFTER POWERING DOWN THE SYSTEM to allow the high voltages to dissipate. Turn off the power before removing or inserting any boards.

To troubleshoot the 16-slot power supply, carry out the following steps:

- Initial checkout

- Indicator light checkout

- Voltage checkout

- Final checkout

- Battery backup checkout

Complete all steps in the order in which they are presented. (The battery backup checkout is only for systems with battery backup.) Failure to do so may result in longer system down time and unnecessary assistance from DGC Field Service. Whenever you replace a unit, repeat the check that indicated a unit was faulty. If the check still indicates the unit is faulty, replace the original unit before continuing. Procedures for replacing FRUs are given in Part 4. The steps for troubleshooting the power supply assume the following conditions:

• The CPU board is in the chassis. (Powering up an unloaded power supply will blow fuse F5 in the VNR unit so do not troubleshoot the power supply without at least the CPU board in the chassis.)

- The load on the power supply is balanced. (You may upset this balance if you remove or add boards while troubleshooting. See the installation data sheets, DGC No. 010-000213, for the load balancing rules.)

- All the electrical connections between units are good.

- The lock switch on the front console is in the UNLOCK position.

If you have any reason to think that these conditions are not met, check them before proceeding.

Figure 6.5 Diagnostic test plug

#### **Initial Checkout**

**1.** Turn power off and unplug the chassis ac line cord from the cabinet.

**2.** Make sure the cabinet is supplying the proper ac line voltage.

3. Plug the line cord back into the cabinet.

**4.** Swing the VNR unit away from backpanel (see *VNR Unit Replacement*, Part 4).

5. Make sure the diagnostic test plug is inserted in the correct location with the "RUN" label up (see Figure 6.5).

**6.** Swing the VNR unit back into position (see *VNR Unit Replacement*, Part 4).

7. Remove the front panel (see *Front Panel Replacement*, Part 4).

8. Turn the power on.

**9.** Look through any open slots on the left side of the chassis and see if all the fans are running. You may need to remove boards from slots 6 and 15 and use a flashlight to see the fans.

**a.** If all four fans are running, reinsert any boards you removed, and go to "Indicator Light Checkout."

**b.** If some, but not all, of the fans are running, replace the faulty fans and make sure the cable connectors to the fans and the console PCB assembly are seated securely. (See *Fan and Fan Module Replacement for 16-Slot Chassis*, Part 4.)

**c.** If none of the fans are running, continue checkout.

10. If you have not replaced a fan:

**a.** Remove the fan module and make sure the cable connectors to the console PCB boards are seated securely (see *Fan Module Replacement for 16-Slot Chassis*, Part 4).

**b.** Reinstall the fan module.

Figure 6.6 Line fuses

**11.** Make sure the internal cable (wiring harness) connectors to the backpanel, the power supply board, and the VNR unit are seated securely (see *VNR Unit Replacement*, Part 4).

**12.** Turn the power off.

**13.** Check the two 15 Amp ac line fuses which screw into the upper left rear corner of the VNR unit (see Figure 6.6).

- a. If the fuses are all right, replace the fan module.

- **b.** If the fuses are blown:

- Replace them if you have NOT already replaced them; otherwise,

- If the fans still do not run, replace the VNR unit.

14. If you cannot get the fans to run after carrying out steps 9 through 13, replace the internal cable (see 16-Slot Wiring Harness Replacement, Part 4).

**15.** If the fans still do not run after carrying out step 14, replace the fan module (see *Fan and Fan Module Replacement for 16-Slot Chassis*, Part 4).

#### **Indicator Light Checkout**

**1.** Turn the power on.

2. Check the indicator lights on the front end of the power supply board (see Figure 6.2). If they are all out, go to "Voltage Checkout"; otherwise, turn the power off and then on again. If any of the lights turn on again, follow the procedure below for the lights which are on. Whenever you replace a unit, repeat this step.

#### **Memory Disaster Light**

**1.** Turn the power off.

2. Check that the diagnostic test plug is in the correct location with the "RUN" label up (see Figure 6.5). If it is, continue to step 3; otherwise:

- a. Reposition the plug.

- **b.** Turn the power on.

- **c.** Check the memory disaster light. If it is on, continue to step 3.

**3.** Replace the power supply board. If the memory disaster light is still on, replace the CPU board.

**4.** If you have already done steps 1 through 3 and the memory disaster light is still on, replace the internal cable (wiring harness).

### **Over-Current Light**

- **1.** Turn the power off.

- 2. Replace the power supply board.

- 3. Turn the power on.

**4.** Check the over-current light. If the light is on, turn the power off and remove any printed circuit board, other than the power supply board.

- 5. Turn the power on.

- 6. Check the over-current light.

**a.** If the light is NOT on, replace the board being sure to insert the correct jumpers (see the appropriate I/O device documentation).

**b.** If the light is on, reinsert the removed board, and repeat steps 4 through 6 with any other printed circuit board you have not already tried removing.

**c.** If you have already done steps a and b and the over-current light is still on, check that the load on the power supply is balanced (see the *Installation Data Sheets*, DGC No. 010-000213, for the load balancing rules).

7. If you have already done steps 1 through 6 and the over-current light is still on, replace the internal cable (wiring harness).

### **Over-Voltage Light**

- **1.** Turn the power off.

- 2. Replace the power supply board.

- 3. If the light is still on, replace the CPU board.

**4.** If you have already done steps 1 through 3 and the overvoltage light is still on, replace the internal cable (wiring harness).

## **Voltage Checkout**

1. Turn the power on.

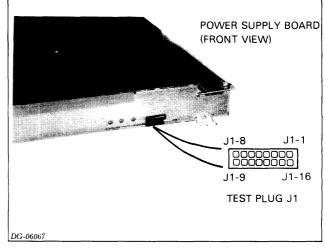

**2.** Check the +5V voltage at test plug J1-15 (see Figure 6.8). If +5V is between 5.10V and 5.20V, go to "Final Checkout"; otherwise, continue the checkout.

**3.** Turn the power off.

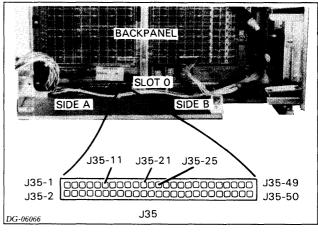

Figure 6.7 Jack 35

Figure 6.8 Test plug

**4.** Short **MEMD** at J35-21 to GND at J35-1 (see Figure 6.7). Before continuing the checkout, make sure you have shorted the correct pins.

- 5. Turn the power on and check the memory disaster light.

- **a.** If the light is NOT on, turn the power off, remove the short, and replace the VNR unit.

**b.** If the light is on, turn the power off, remove the short, and then turn the power on.

- Check the **-11V** voltage at J35-25 (see Figure 6.7).

- If -11V is NOT between -11.0V and -12.5V (-30VNR not ok), check the VREF at test plug J1-14 (see figure 6.8). If VREF is 5.8V, replace the VNR unit; otherwise, replace the power supply board.

- If -11V is between -11.0V and -12.5V (-30VNR ok), check the HVS voltage at test plug J1-4 (see Figure 6.8). If HVS is greater then 2.9V, replace the power supply board; otherwise, replace the VNR unit.

**6.** Recheck the +5V voltage at test plug J1-15 (see Figure 6.8). If it is between 5.10V and 5.20V, go to "Final Checkout"; otherwise, try replacing the internal cable (wiring harness). If this does not work, call DGC Field Service.

Figure 6.9 Line fuses

## **Final Checkout**

#### 1. Turn power on.

2. Check the power on light on the front console.

a. If the light is on, continue to step 3 of this checkout.

b. If the light is NOT on, check the **ONLED-P** voltage at J35-11 (see Figure 6.7).

- If **ONLED-P** is 3V or greater, replace the power supply board; otherwise, replace the console PCB assembly.

- If the light still is not on, replace the fan module, and if this does not correct the problem, replace the internal cable (wiring harness).

- 3. Turn the power off and see if the fans stop.

- a. If the fans stop:

- Go to "Battery Backup Checkout" if the system has battery backup.

- Go to Chapter 5, *Computer Self-Test*, if the system does not have battery backup.

- **b.** If the fans do NOT stop:

- Make sure the LOCK switch is in the UNLOCK position. If the fans still do not stop, check the **PWR FAIL** voltage at test plug J1-3 (see Figure 6.8).

- If **PWR FAIL** is NOT less than 0.4V, replace the fan module.

- If **PWR FAIL** is less than 0.4V, check **PON** at test plug J1-11 (see Figure 6.8). If **PON** is less than 0.4V, replace the VNR unit; otherwise, replace the power supply board.

### **Battery Backup Checkout**

This procedure, used when a system has battery backup, will not discharge the battery a significant amount. Note that it takes 16 hours for the battery to fully recharge.

**1.** Turn the power on and unplug the chassis ac line cord from the cabinet.

**2.** Check the + **12 MEM** voltage at location J35-3 (see Figure 6.7).

**a.** If this voltage is greater than 11.0 volts and remains constant for more than 1 minute, continue to step 3; otherwise,

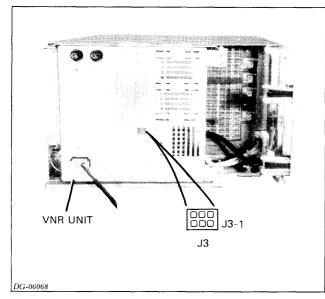

- **b.** Check the **BAT** + voltage at jack J3-1 (see Figure 6.9).

- If **BAT** + is greater than 12V, replace the power supply board.

- If **BAT** + is NOT greater than 12V, then measure the voltage difference between J3-5 and J3-6 (see Figure 6.9). If it is greater than one volt, replace the battery; otherwise, replace the VNR unit.

- 3. Check the battery backup light on the front console.

**a.** If this light is on, plug the power cord into the ac source and then go to Chapter 5, *Computer Self-Test*.

**b.** If the light is NOT on, replace the power supply board, and if the light still does not turn on, replace the console PCB assembly.

4. Plug the ac line cord back into the cabinet.

## TROUBLESHOOTING 5-SLOT POWER SUPPLY

**WARNING:** The power supply board generates dangerously high voltages. DO NOT ATTEMPT TO MEASURE VOLTAGES INSIDE IT. Before you remove the cover on the power supply board WAIT AT LEAST 5 MINUTES AFTER POWERING DOWN THE SYSTEM to allow the high voltages to dissipate. Turn off the power before removing or installing any boards.

To troubleshoot the 5-slot power supply, carry out the following steps:

- Initial checkout

- Final checkout

- Battery backup checkout

Complete all steps in the order in which they are presented. (The battery backup checkout is only for systems with battery backup.) Failure to do so may result in a longer system down time and unnecessary assistance from DGC Field Service.

Whenever you replace a unit, repeat the check which indicated that unit was faulty. If the check still indicates the unit is faulty, replace the orginal unit before continuing. Procedures for replacing field replaceable units are given in Part 4.

The steps for troubleshooting the power supply assume the following conditions:

- The CPU board is in the chassis. (An unloaded power supply will not produce regulated outputs, so do not troubleshoot the system without at least the CPU board in the chassis.)

- All the electrical connections between units are good.

- The lock switch on the front console is in the UNLOCK position.

Figure 6.10 Line fuse for 5-slot power supply

If you have any reason to think that these conditions are not met, check them before proceeding.

### Initial Checkout

**1.** Turn the power off and unplug the chassis ac line cord from cabinet.

**2.** Make sure the ac line source in the cabinet is supplying the proper ac line voltage.

- 3. Plug the line cord back into the cabinet.

- 4. Turn the power on.

**5.** Look through any open slot and see on the left side of the chassis if both fans are running. You may need to remove the board from slot 4 and use a flashlight to see the fans.

**a.** If both fans are running, reinsert the board you removed, and go to "Final Checkout."

**b.** If only one fan is running, replace the faulty fan and make sure the internal cable connectors to the fans and the console PCB assembly are seated securely.

c. If neither fan is running, continue with this checkout.

**6.** If you have not replaced a fan, make sure the internal cable (wiring harness) connectors to the console PCB assembly are seated securely (see 5-Slot Wiring Harness Replacement, Part 4).

7. Make sure the internal cable (wiring harness) connectors to the backpanel and the power supply board are seated securely.

8. Switch the power off.

**9.** Check the 7 Amp ac line fuse which screws into the left rear corner of the power supply board and extends through a cutout in the backpanel (see Figure 6.10).

**a.** If the fuse is all right, replace the power supply board.

**b.** If the fuse is blown:

- Replace it if you have NOT already replaced it; otherwise,

- Replace the power supply board.

**10.** If you cannot get the fans to run after carrying out steps 1 through 9, replace the internal cable (wiring harness) (see 5-Slot Wiring Harness Replacement, Part 4).

### **Final Checkout**

1. Turn power on.

- 2. Check the power on light on the front console.

- **a.** If the light is on, continue to step 3 of this checkout. **b.** If light is NOT on:

- Replace the power supply board.

- If the light still does not go on, reseat the internal cable (wiring harness) connectors to the the console PCB assembly. If this does not correct the problem, first replace the console PCB assembly, and then the internal cable.

3. Turn the power off and see if the fans stop.

- **a.** If the fans stop:

- Go to "Battery Backup Checkout" if the system has battery backup.

- Go to Chapter 5, *Computer Self-Test*, if the system does not have battery backup.

- **b.** If the fans do NOT stop, replace the power supply board. If this does not correct the problem, first try reseating the internal cable (wiring harness) connectors, and then replace the internal cable.

### **Battery Backup Checkout**

This procedure, used when a system has battery backup, will not discharge the battery a significant amount. Note that it takes 24 hours to recharge the battery completely.

**1.** Turn the power on and unplug the chassis ac line cord from the cabinet.

2. Check the +12 MEM voltage at backpanel pin B47.

**a.** If this voltage is greater than 11.3 volts and remains constant for more than 5 minutes, go to step 3 of this checkout; otherwise, continue with step b.

**b.** Most likely the battery is bad or the battery charger on the power supply board is not operating properly. If you have reason to suspect the battery is bad, replace it; otherwise, replace the power supply board. Note that an unused battery lasts about 3 1/2 years at 23 deg.C and its life expectancy decreases greatly with increases in operating temperature. A battery can be used for about 200 cycles.

3. Check the battery backup light on the front console.

**a.** If this light is on, plug the line cord back into the cabinet and go to Chapter 5, *Computer Self-Test*.

**b.** If the light is NOT on, replace the power supply board, and if the light still does not go on, replace the console PCB assembly.

**4.** Plug the ac line cord back into the cabinet.

**Data General Corporation**

3

# Chapter 7 DIAGNOSTIC TESTING

| Program Name                     | DTOS<br>Mnemonic | Program Description                                                                                                                                                                                                                                                              |

|----------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOVA 3 Reliability<br>Test Short | N3MORT S         | This reliability program consists of<br>a series of individual programs that<br>test the interactive capabilities of<br>the CPU; the CPU-resident<br>real-time clock, asynchronous<br>interface, and memory; and the<br>1/O tester board.                                        |

| NOVA 4 Logic Test                | N4LGCTST         | This program tests the logic used<br>by the CPU to implement the<br>instruction set. It also performs<br>minimum level testing of the CPU<br>I/O instructions, system terminal<br>I/O, and the program interrupt<br>facility.                                                    |

| NOVA 4 EXERCISER                 | N4EXER           | This program exercises the CPU<br>instruction set and tests the CPU's<br>reliability.                                                                                                                                                                                            |

| NOVA 4/C Memory<br>Diagnostic    | N4CMD            | This program consists of a series<br>of tests that check main memory<br>for faulty address decoding,<br>memory accessibility, sense<br>amplifier recovery, refresh<br>sensitivity, interaction between<br>memory elements, memory<br>access time and memory cell<br>reliability. |

| Basic Input/Output<br>Test       | AIODCH F         | This program requires the presence of the multi-mode I/O tester board No. 005-004283. It tests the I/O instructions, the operation of the data channel and the real-time clock.                                                                                                  |

| Real-Time Clock Test             | RTC TST          | This program tests the operation of the real-time clock.                                                                                                                                                                                                                         |

Table 7.1 Reliability and diagnostic test program summary

Successful completion of the self-test indicates that the main portion of the NOVA 4/C computer is operating properly. This means that the reliability and diagnostic test programs described in Table 7.1 can be loaded into main memory and used to:

- Detect faulty field replaceable units during troubleshooting;

- Verify that the computer is operating properly during initial checkout or after repair.

The programs listed in Table 7.1 are available on either:

- Magnetic tape or diskette (NOVA 4 DTOS)

- Data General field service cassette

Loading procedures for DTOS (Diagnostic Operating System) appear in Appendix B. Procedures for using the field service cassette appear in Appendix C.

## TROUBLESHOOTING FLOWCHART

The troubleshooting flowchart, Figure 7.1, leads you through sequences of reliability and diagnostic tests that will both isolate faulty field replaceable units and verify the proper operation of the NOVA 4/C computer. It assumes that the programs are loaded and run under the control of DTOS and specifies the DTOS commands to be used. If a DTOS loading device (i.e., magnetic tape unit or disc drive) is not present in the system or is inoperable, the flowchart can still be used by running the programs in the sequences indicated, using the field service cassette.

**NOTE:** Detailed information concerning DTOS and DTOS commands appears in DIAGNOSTIC OPERATING SYSTEM, TECHNICAL MANUAL (DG No. 015-000056), and DTOS SUMMARY (DG No. 015-000082).

Throughout the flowchart, action recommendations following each program test are made solely on a pass/fail basis. To determine if a test passed, refer to the sample program run summary for that test at the end of this chapter. Each summary describes both the operator input and the program output, i.e., the information that will be printed (displayed) by the system terminal when the specified test passes.

When the flowchart specifies the replacement of a field replaceable unit (FRU), proceed as follows:

- Power down the system