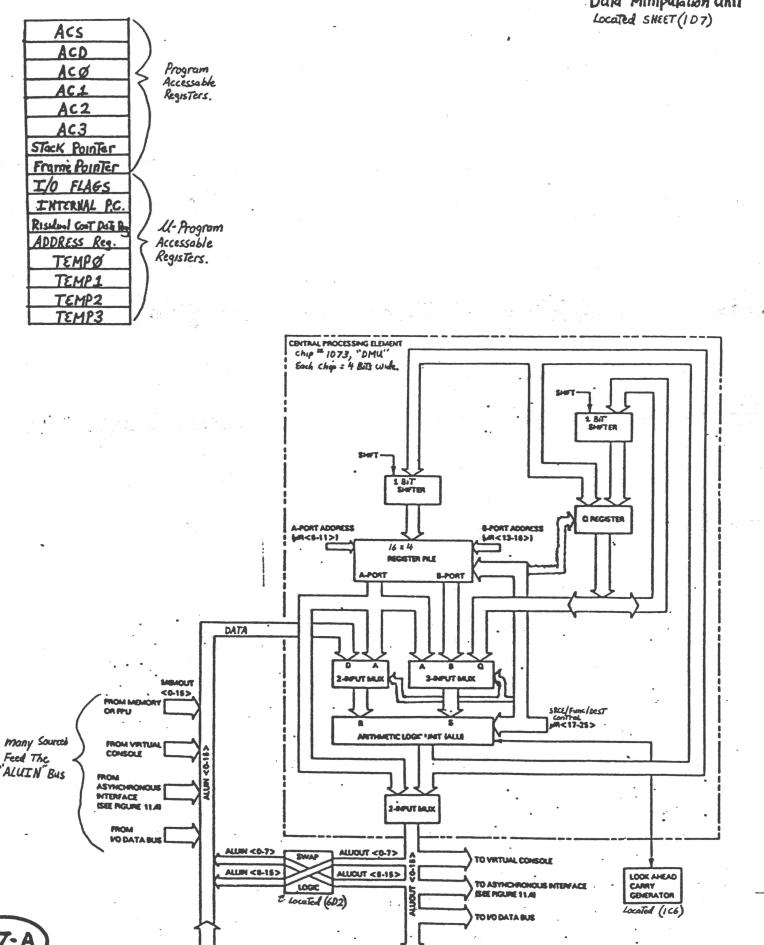

Data Minipulation Unit

TO CONTROL PROCESSOR

FROM CONTROL PROCESSOR

## MEMORY ADDRESSING (For Read or Write)

Current Micro-Cycles ALUOUT Address Data is latched into "Memin Latches" (2D8) during time #4 of BMEMCLK. see CHART (2D1).

During Time #3, Next Micro-Cycle's CMEMO enables CMEMSTART (12B8) to (2A/B6). CMEMO also enables AND-NOR GATE 28-0 (2B5) into F/F 26-E.

At start of Time #4, BMEMCLK latches in ALUOUT Address into Latches and generates CPUMEMSTART (2A/B5) to (2B7) FOR start Pulse to Memory, and enables F/F 26-E (2B4) for "MEMDRIVE" to (2D7). Thus enabling the ADDRESS OUT to memory.

## MEMORY WRITE

At the start of the next Micro-Cycle CPUMEMSTART is still high (2A/B5) during Time #5, and is applied to Driver 28-E (2B6/7) as well as to NAND 28-J (2A5). MEMDRIVE (2D7) is also still enabled at this time.

During Time #5, WIR1 (2B8) generates MEMWRITE (2B6) and enables NAND 20-J (2A5) to enable "Rightwrite" across inverter 20-Y (2A5) and out to AND-NOR GATE 20-0 (2B5).

Data for writing to memory is alo now available on inputs on MEMIN Latches (2D8) from ALUOUT (6-15)

For ALUOUT (0-5) to be enabled onto latch inputs; Rightwrite (2A5) Low to NAND 28-J (11C5) thus disabling MAPOE High (11C/B4). MAPOE High, enables Driver 18-0 (11D5) thus enabling ALUOUT (0-5) to latches.

At Start of Time #6 CPUMEMSTART (2B7) goes Low. (Memory has already received the write CMD). ALUOUT DATA is latched (2D8) and F/F 26-E (2B4) stays set to enable the DATAOUT to memory via MEMDRIVE (2D/).

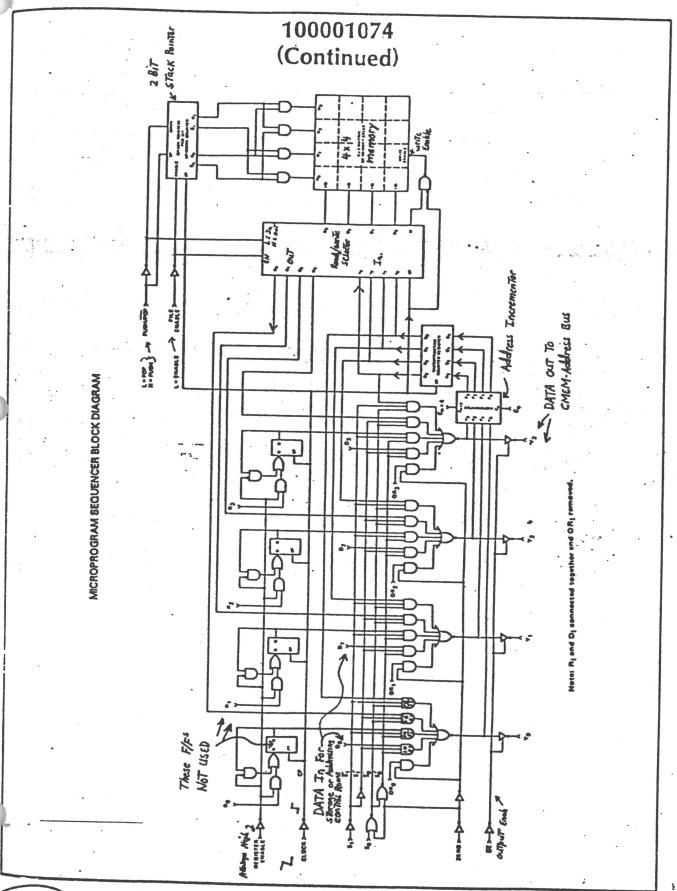

## 100001074 (Continued)

ADDRESS SELECTION

11

OCTAL S<sub>1</sub> S<sub>0</sub> SOURCE FOR Y OUTPUTS SYMBOL

0 L L Microprogram Counter µPC

1 L H Register REG

2 H L Push-Pop stack STKO

3 H H Direct inputs Di

L = Low

9 SYNCHRONOUS STACK CONTROL

FE PUP PUSH-POP STACK CHANGE

H X No change

Increment stack pointer, then push current PC onto STK0

L L Pop stack (decrement stack pointer)

OUTPUT AND INTERNAL NEXT-CYCLE REGISTER STATES

Internal 15-12 10,19.20 PRINCIPLE S1. So. FE. PUP REG STKO STK1 STK2 STK3 Your COMMENT USE 0000 Rb Rc Rc Rd Ra Rb · End Pop Stack N+1 Loop 0001 Rc Rb Set-up Push µPC Ra Rc J J+1 001X Ra Ra Rb Rb Rc Rc Rd Rd Continue N+1 J K+1 0100 Ra Rb Rb Rc Rc Rd Pop Stack; Use AR for Address End Loop J K+1 0101 Rb Ra Push µPC; JSR AR N+1 Jump to Address in AR J K+1 0 1 1 X Ra Rb Rc Rd Jump to Address in AR JMP AR Rc Ra Rb J Ra+1 1000 Ra Rb Rь Rc Rd Jump to Address in STKO: RTS N+1 Rc 1001 J Ra+1 Rd Jump to Address in STKO; Ra Rb Rc Push µPC J Ra+1 101X Ra Ra Rb Rb Rc Rc Rd Stack Ref Jump to Address in STKO Rd (Loop) J D+1 Rb Rc 1100 Ra Rb Rc Rd Rd Pop Stack: N+1 Jump to Address on D Loop J D+1 1101 Ra Яb Rd Jump to Address on D; JSR D N+1 Ra Rb Rc Push µPC 111X Ra Ra Rb Rb Rc Rc Rd Rd Jump to Address on D N+1 D+1

X = Don't care, 0 = LOW, 1 = HIGH, Assume Cn = HIGH Note: STKO is the location addressed by the stack points

10-35

488-A