**Programmer's Reference Series**

# Peripherals

DataGeneral

# NOTICE

Data General Corporation (DGC) has prepared this manual for use by DGC personnel, licensees, and customers. The information contained herein is the property of DGC and shall not be reproduced in whole or in part without DGC's prior written approval.

Users are cautioned that DGC reserves the right to make changes without notice in the specifications and materials contained herein and shall not be responsible for any damages (including consequential) caused by reliance on the materials presented, including, but not limited to typographical, arithmetic, or listing errors.

NOVA, INFOS, and ECLIPSE are registered trademarks of Data General Corporation, Westboro, Massachusetts. DASHER, microNOVA, and ECLIPSE MV/8000 are trademarks of Data General Corporation, Westboro, Massachusetts.

> Ordering No. 014-000632 <sup>ac</sup>Data General Corporation, 1979, 1980 All Rights Reserved Printed in the United States of America Rev. 01, October 1980

# PREFACE

The Programmer's Reference Manual for Peripherals is designed as a companion volume to the Programmer's Reference Manuals for the NOVA line and ECLIPSE Computers. It furnishes the general principles and the specific details needed to program input/output (I/O) transfers between standard DGC peripherals and all DGC computers.

This manual consists of several sections. Section I introduces the theory of I/O programming on DGC computers and presents several complete examples of I/O programs. The remaining sections of the manual deal with the various families of peripherals supplied by Data General Corporation. Separate chapters in each section provide the specific information necessary to program the individual peripherals in each family. Section II covers terminals; Section III covers hard copy devices. Section IV deals with magnetic tape storage devices, including industry-standard magnetic tape units and the DGC cassette. Section V covers fixed head discs, disc cartridges, and disc packs. Section VI describes analog-to-digital and digital-to-analog conversion with the Analog Data Conversion System. The appendices contain a number of reference tables which supply information about device codes, character codes, and timing figures needed for I/O operations.

Before reading this manual, the programmer should have a basic understanding of the programming of DGC computers, as described in the Programmer's Reference Manual for the NOVA line Computers (DGC 015-000023) and, where appropriate, in the Programmer's Reference Manual for the ECLIPSE Computer (DGC 015-000024). A familiarity with the operation of the DGC assembler, as described in the Assembler Manual (DGC 093-000017), is also recommended, as the programming examples are written in assembly language.

Additional information, of a more technical nature, may be found in the Interface Manual (DGC 015-000031), which describes the technical operation of the I/O bus and explains how to interface a nonstandard peripheral to any of the DGC computers.

As portions of this manual are updated, they are printed according to new typesetting specifications. This means some sections are presented in a different style than others. We ask our readers' indulgence for this unavoidable defect.

# **CONTENTS**

| Ś | E | C | T | 0 | N | J | I |

|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |

1

1

2

2

5

5

7

9

1

# I/O PROGRAMMING

**OVERVIEW OF INPUT/OUTPUT**

INTRODUCTION TYPES OF INFORMATION

TYPES OF INFORMATION TRANSFER

PROGRAM INTERRUPT FACILITY

3 SUMMARY

# 5 I/O INSTRUCTION SET

INTRODUCTION THE TYPICAL CONTROLLER INSTRUCTION FORMAT

INSTRUCTIONS

# **13 PROGRAM INTERRUPT FACILITY**

- 13 INTRODUCTION

- 13 OPERATION

- 16 INSTRUCTIONS

- **17 PRIORITY INTERRUPTS**

- 23 DATA CHANNEL FACILITY

- 23 INTRODUCTION

- 23 CONTROLLER STRUCTURE

- **24 TRANSFER SEQUENCE**

- 24 DATA CHANNEL MAP SELECTION

- 25 PROGRAMMING

- 27 TIMING

- 27 INTRODUCTION

- 27 DIRECT PROGRAM CONTROL

- 28 DATA CHANNEL CONTROL

# **31 PROGRAM EXAMPLES**

- 31 INTRODUCTION

- 32 EXAMPLE ONE

- 34 EXAMPLE TWO

- **37 EXAMPLE THREE**

- 47 EXAMPLE FOUR

# SECTION II TERMINALS

- **1** INTRODUCTION TO TERMINALS

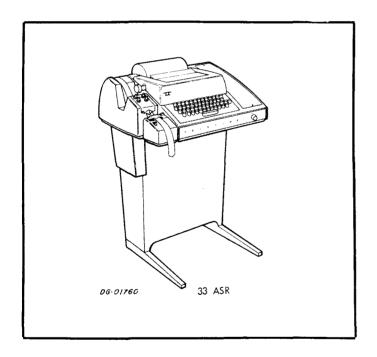

- **3 TELETYPES**

- 3 INTRODUCTION

- 4 INSTRUCTIONS

- 5 **PROGRAMMING**

- 5 TIMING

- 5 ADDITIONAL NOTES

- 7 **PROGRAMMING EXAMPLES**

- 9 DGC DISPLAY 6012

- 9 INTRODUCTION

- **10 INSTRUCTIONS**

- 11 CONTROL CHARACTERS

- 11 CONTROL KEYS

- 14 **PROGAMMING**

- 14 TIMING

- **15 ADDITIONAL NOTES**

# SECTION III HARD COPY

**1** INTRODUCTION TO HARD COPY PERIPHERALS

# **3 PAPER TAPE READER**

- **3** INTRODUCTION

- 4 INSTRUCTIONS

- 4 **PROGRAMMING**

- 4 TIMING

- 4 ADDITIONAL NOTE

- 5 **PROGRAMMING EXAMPLES**

## PAPER TAPE PUNCH

- INTRODUCTION

- 7 8 **INSTRUCTIONS**

- 8 PROGRAMMING

- 8 TIMING

7

- 8 **ADDITIONAL NOTES**

- 9 **PROGRAMMING EXAMPLES**

#### 11 **CARD READERS**

- 11 INTRODUCTION

- 12 INSTRUCTIONS

- 13 PROGRAMMING

- 14 TIMING

- **ERROR CONDITIONS** 14

- 15 **PROGRAMMING EXAMPLES**

#### 17 **DASHER LP2 PRINTER**

- 17 **INTRODUCTION**

- 19 **CODE RECEPTION**

- 23 PLOTTING

- 25 **DOWN-LINE-LOADING A CHARACTER SET**

- 30 SUMMARY OF ESCAPE SEQUENCES

- 31 **INSTRUCTIONS FOR PROGRAMMED I/O CONTROLLER**

- 32 **INSTRUCTIONS FOR DATA CHANNEL LINE PRINTER CONTROLLER**

- 34 **CONTROLLER PROGRAMMING**

- 35 **4034 SERIES PRINTERS**

- 35 **INTRODUCTION**

- 37 INSTRUCTIONS

- 38 PROGRAMMING

- 39 **CONTROL CHARACTERS**

- 40 TIMING

- 41 **PROGRAMMING EXAMPLE**

- COMMERCIAL I/O SUBSYSTEM, MODELS 4215-19, 4244-45 43

- 44 INTRODUCTION

- 44 INSTRUCTIONS

- 46 **PROGRAMMING OVERVIEW**

- 47 HORIZONTAL TABBING

- 48 **VERTICAL TABBING**

- 54 **PROGRAMMABLE INTERVAL TIMER**

- 55 INSTRUCTIONS

# 57 INCREMENTAL PLOTTERS

- 57 INTRODUCTION

- 58 INSTRUCTIONS

- 60 PROGRAMMING

- 60 TIMING

- 60 ADDITIONAL NOTES

- 60 **PROGRAMMING EXAMPLE**

# SECTION IV MAGNETIC TAPES

- **1** INTRODUCTION TO MAGNETIC TAPES

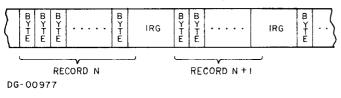

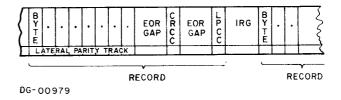

- **1 TAPE TRANSPORT SUBSYSTEMS**

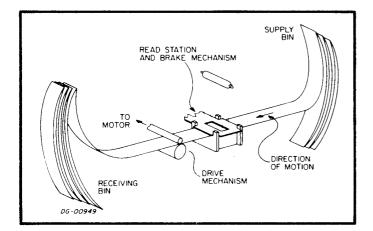

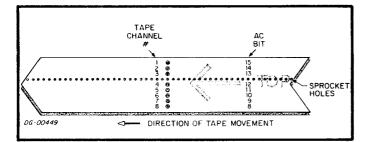

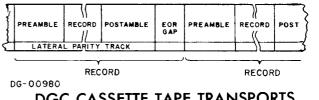

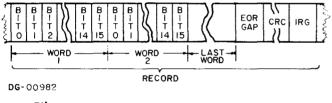

- 2 DGC CASSETTE TAPE TRANSPORTS

- 4 SUMMARY OF SPECIFICATIONS

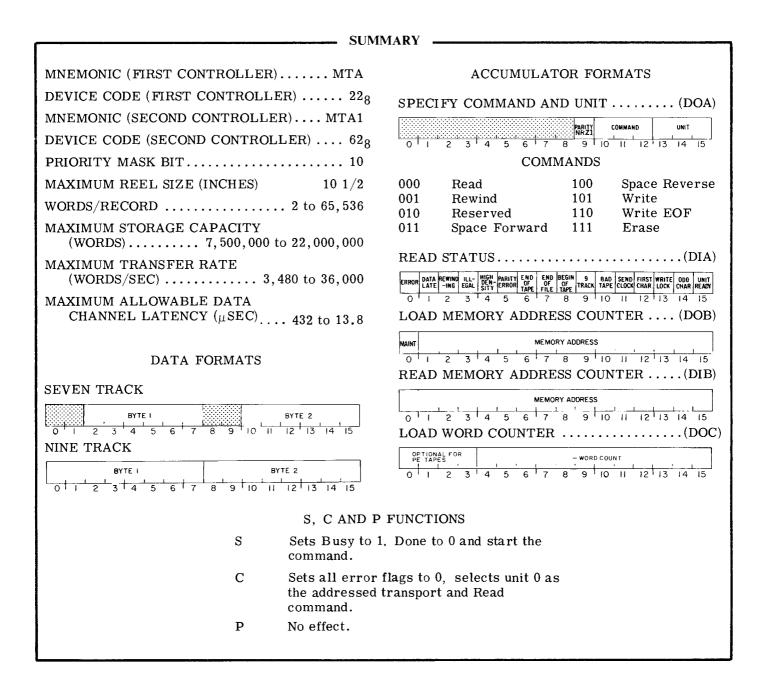

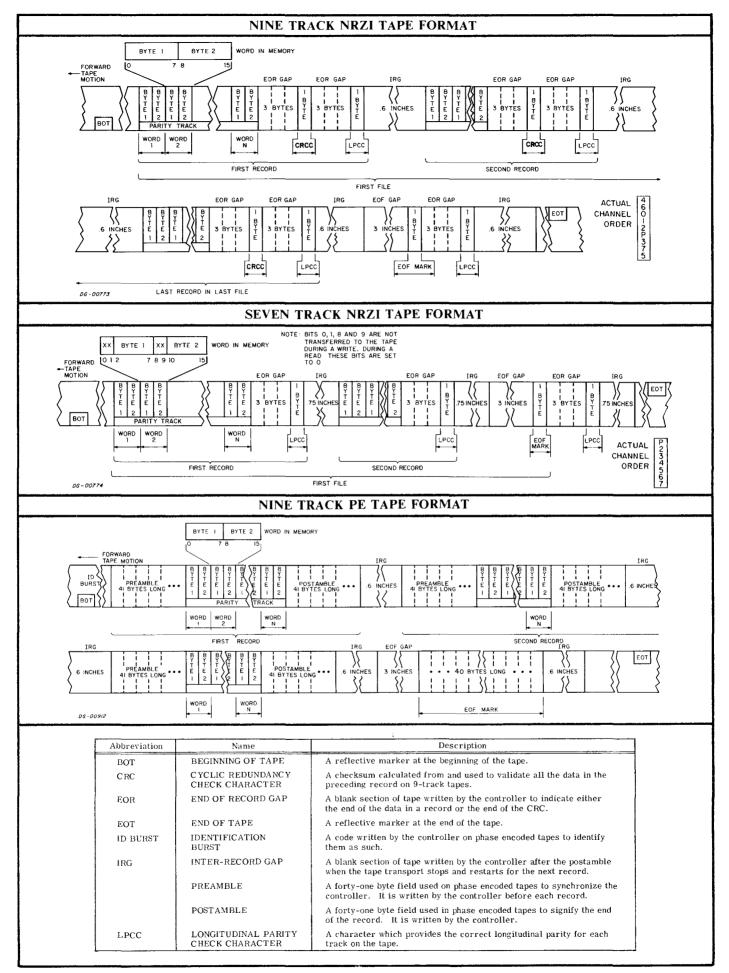

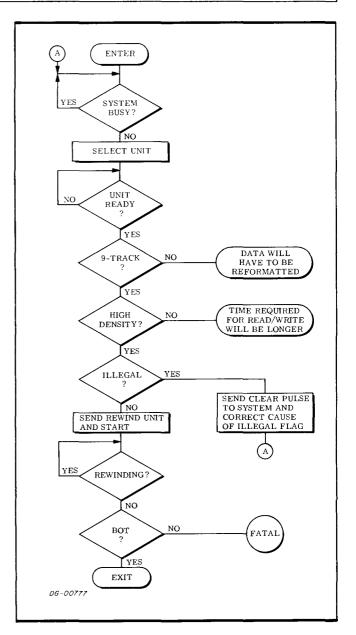

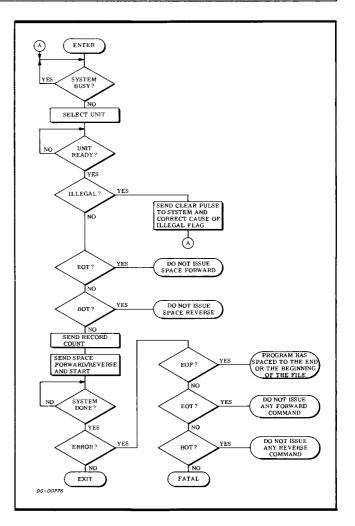

- 5 MAGNETIC TAPE TRANSPORTS, SERIES 4030, 4196, 6020

- 7 INTRODUCTION

- 7 INSTRUCTIONS

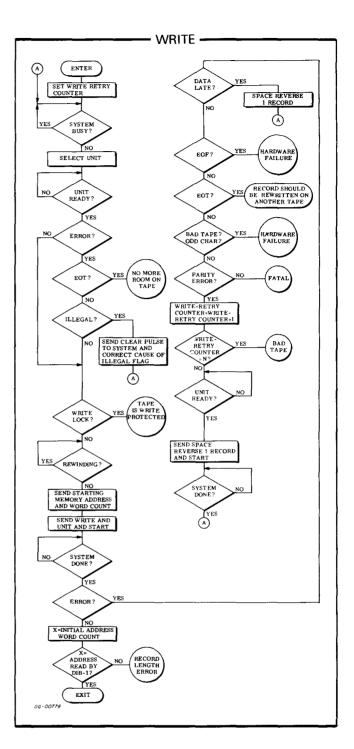

- 10 **PROGRAMMING**

- 14 TIMING

- **14 ERROR CONDITIONS**

- **15 MAGNETIC TAPE TRANSPORTS, SERIES 6026**

- 16 INTRODUCTION

- **16 CONTROLLER REGISTERS**

- 16 INSTRUCTIONS

- 20 PROGRAMMING

- 24 TIMING

- 24 ERROR CONDITIONS

# 25 DGC CASSETTE SUBSYSTEM

- 25 INTRODUCTION

- 25 INSTRUCTIONS

- 29 PROGRAMMING

- 33 TIMING

- **33 ERROR CONDITIONS**

# SECTION V DISCS

#### **INTRODUCTION TO DGC DISCS** 1

- 2 **DATA FORMATS ON DGC DISCS**

- 2 ACCESSING

- 3 DGC DISC SUBSYSTEMS

- 4 SHARED DISC CONSIDERATIONS

#### 5 FIXED HEAD DISC SUBSYSTEM

- 5 **INTRODUCTION**

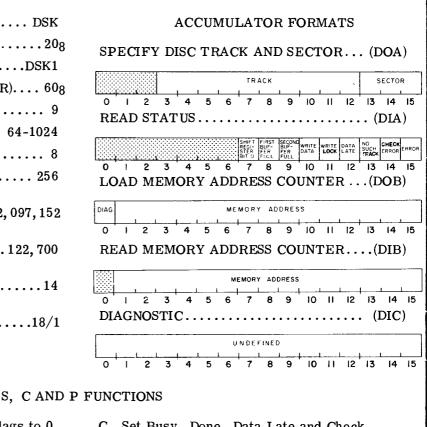

- 6 **INSTRUCTIONS**

- 7 PROGRAMMING

- 9 TIMING

- 9 **DISC FORMAT**

- 10 **ERROR CONDITIONS**

#### 11 THE 4047A AND 4047B DISC CARTRIDGE SYSTEMS

- 11 INTRODUCTION

- 11 **INSTRUCTIONS**

- 15 PROGRAMMING

- 19 TIMING

- 20 **ERROR CONDITIONS**

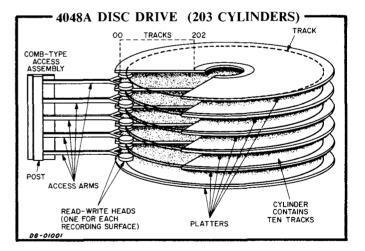

#### 21 **THE 4048A DISC PACK SUBSYSTEM**

- 21 **INTRODUCTIONS**

- 22 INSTRUCTIONS

- 25 PROGRAMMING

- 29 TIMING

- 29 **ERROR CONDITIONS**

- 31 THE 4057A DISC PACK

- 31 INTRODUCTION

- 32 INSTRUCTIONS

- 35 PROGRAMMING

- 39 TIMING

- 39 **ERROR CONDITIONS**

#### 43 THE 4231A DISC PACK SUBSYSTEM

- 44 INTRODUCTION

- 44 INSTRUCTIONS

- 47 PROGRAMMING

- 50 FORMAT

- TIMING

- 50 50 **ERROR CONDITIONS**

### 53 CARTRIDGE DG/DISC SUBSYSTEM MODELS 6045, 6050, (

- 54 INTRODUCTION

- 54 **CONTROLLER REGISTERS**

- 54 54 57 INSTRUCTIONS

- PROGRAMMING

- FORMATTING 60

- 60 TIMING

- **ERROR CONDITIONS**

- 61 63 **MULTIPLE DRIVES**

- 64 **DUAL PROCESSOR CONSIDERATIONS**

#### 69 6030 SERIES DG/DISKETTE SUBSYSTEM

- 70 INTRODUCTION

- 70 **CONTROLLER REGISTERS**

- 70 INSTRUCTIONS

- 73 PROGRAMMING

- 76 FORMATTING

- TIMING

- 76 77 **ERROR CONDITIONS**

- 79 **MULTIPLE DRIVES**

- 80 **DUAL PROCESSOR CONSIDERATIONS**

- 85 4234 SERIES 10MB CARTRIDGE DISC SUBSYSTEM

- 86 INTRODUCTION

- 86 86 **CONTROLLER REGISTERS**

- INSTRUCTIONS

- 89 PROGRAMMING

- 92 FORMATTING

- 92 FORMATTING 92 TIMING 93 ERROR CONDITIONS 95 MULTIPLE DRIVES

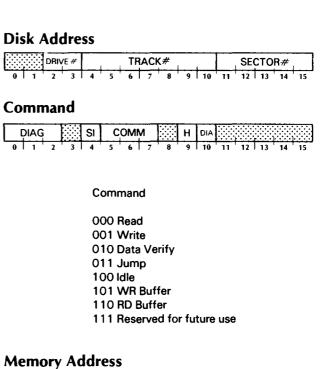

# 97 6060 SERIES DG/DISC STORAGE SUBSYSTEM

- 98 INTRODUCTION

- **99 CONTROLLER REGISTERS**

- 99 INSTRUCTIONS

- **104 PROGRAMMING DETAILS**

- 110 FORMATTING

- 110 TIMING

- **111 DETAILED COMMAND DESCRIPTIONS**

- 112 FAULT FLAGS

- 115 **ERROR CONDITIONS**

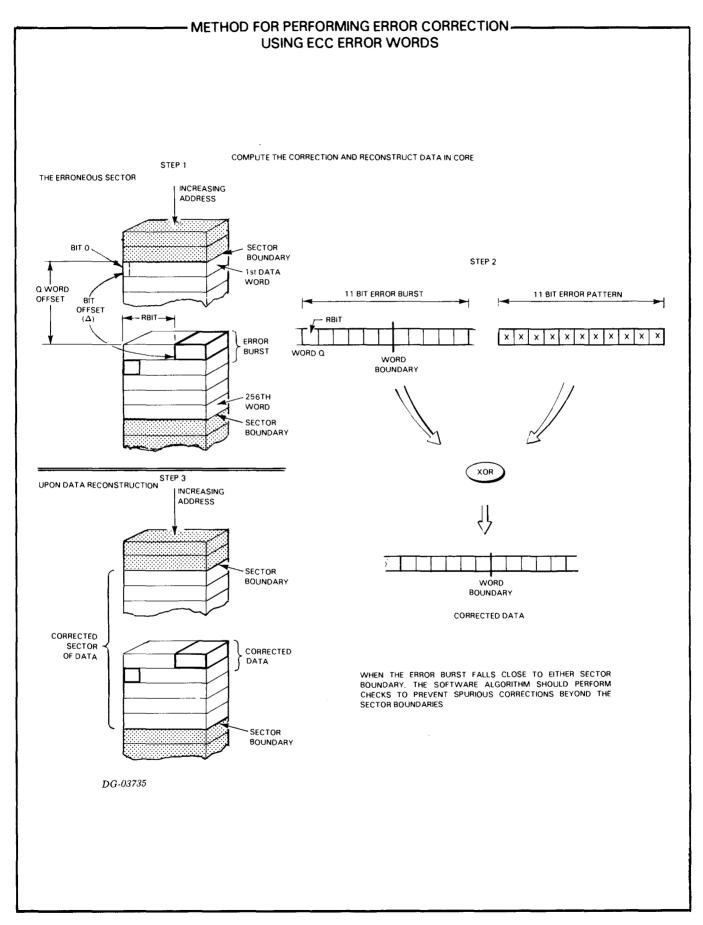

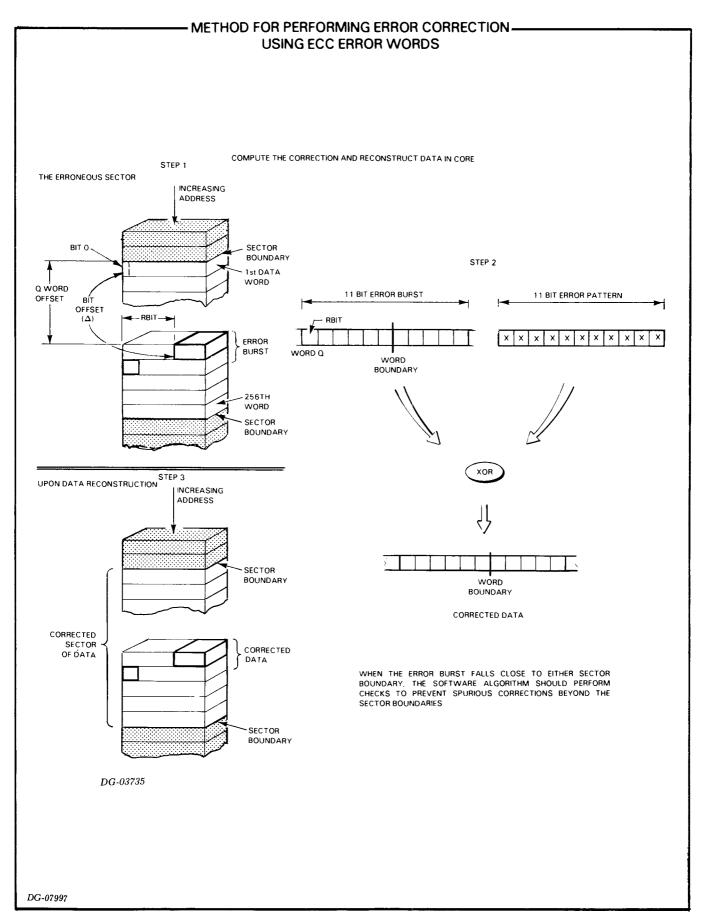

- **116 DATA ERROR CORRECTION**

- 121 6063-6065 SERIES FIXED HEAD DISC SUBSYSTEM

- 122 INTRODUCTION

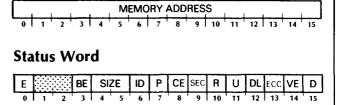

- **122 CONTROLLER REGISTERS**

- **123** INSTRUCTIONS

- **126 COMMAND QUEUE FORMAT**

- 127 PROGRAMMING

- **128 STATUS CHECKING**

- 128 TIMING

- **129 ERROR CONDITIONS**

- **130 DUAL PROCESSOR CONSIDERATIONS**

- **131 DATA ERROR CORRECTION**

- 137 6070 SERIES CARTRIDGE DG/DISC SUBSYSTEM

- 138 INTRODUCTION

- **138 CONTROLLER REGISTERS**

- **138** INSTRUCTIONS

- 142 PROGRAMMING

- 145 FORMATTING

- **146 DIAGNOSTIC MODE**

- 146 TIMING

1

13

- **146 ERROR CONDITIONS**

- 149 MULTIPLE DRIVES

- **150 DUAL PROCESSOR CONSIDERATIONS**

# SECTION VI ANALOG/DIGITAL DIGITAL/ANALOG

## **INTRODUCTION TO DGC A/D AND D/A SUBSYSTEMS**

- ANALOG AND DIGITAL DATA

- DATA ACCURACY

# 5 4120 SERIES ANALOG/DIGITAL CONVERSION SUBSYSTE/

- 5 **CONFIGURATIONS**

- 7 **OPERATION**

- 9 INSTRUCTIONS: SINGLE CONVERSION MODE

- 11 **PROGRAMMING: SINGLE CONVERSION MODE**

- 12 INSTRUCTIONS: DATA CHANNEL MODE

- 16 **PROGRAMMING: DATA CHANNEL MODE**

- 17 PROGRAMMING: SINGLE CONVERSION MODE WITH DATA

- CHANNEL OPTION

- 17 TIMING CONSIDERATIONS

## 19 4180 SERIES DIGITAL/ANALOG CONVERSION SUBSYSTEM

- **19 CONFIGURATIONS**

- 19 OPERATION

- 20 INSTRUCTION: D/A

- 21 **PROGRAMMING: D/A**

- 22 SCOPE CONTROL OPTION

- 23 INSTRUCTIONS: SCOPE CONTROL

- 23 PROGRAMMING: SCOPE CONTROL

- APPENDIX A I/O DEVICE CODES AND DATA GENERAL MNEMONICS

- APPENDIX B OCTAL AND HEXADECIMAL CONVERSION

- APPENDIX C ASCII-128 CHARACTER CODES EBCDIC CHARACTER CODES

APPENDIX D NOVA LINE COMPUTERS INSTRUCTION EXECUTION TIM ECLIPSE COMPUTER INSTRUCTION EXECUTION TIMES

APPENDIX E CODING AIDS

÷...\*

# **SECTION I**

# I/O PROGRAMMING

| • | OVERVIEW OF INPUT/OUTPUT   |

|---|----------------------------|

| • | I/O INSTRUCTION SET        |

| ٠ | PROGRAM INTERRUPT FACILITY |

| • | DATA CHANNEL FACILITY      |

| ٠ | TIMING                     |

• PROGRAMMING EXAMPLES

# **OVERVIEW OF INPUT/OUTPUT**

### INTRODUCTION

Input/output is the process of moving information in a computer system between the central processing unit (CPU) and peripherals such as card readers, line printers, terminals and disc units. Some peripherals, such as card readers, enter information into the system. Some, such as line printers, transfer information out of the system. Some, such as terminals, transfer information in both directions; and others, such as disc units, store information within the system. Peripherals, therefore, can serve two main purposes, they provide the computer with a means of communicating with its surroundings, and they supplement main memory with secondary storage.

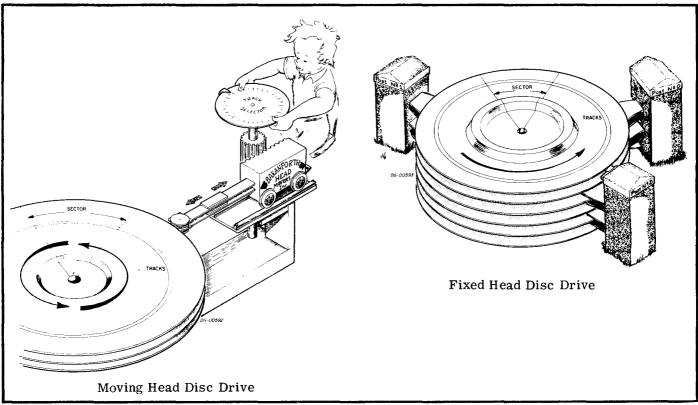

A peripheral generally consists of two units, a device and a controller, but it may also include an adapter. The device, sometimes called a drive, a transport or a terminal, is the unit with which information is read, written, stored, or processed. For example, a terminal's keyboard "reads" information; a plotter "writes" information; a magnetic tape transport "stores" information; and an A/D converter "processes" information.

The controller is the interface between the computer and the device, interpreting commands from the computer to the device and passing information between them. For example, a moving-arm disc controller can translate the track address received from the computer into positional commands for the disc drives access mechanism. Once the access mechanism positions the read/write heads, the controller translates the data words it receives from the computer into the sequence of bits required by the disc drive.

The adapter is an additional unit required by some peripherals to complete the communications link between the device and the controller. It performs functions which are similar to those performed in either the device, the controller, or both. Since the adapter cannot be accessed by the programmer, it is usually transparent.

The communications channel through which all information passes between the computer and the controllers is called the Input/Output (I/O) bus. The central portion of the I/O bus is a 16-bit wide, bidirectional shared data bus. Since this bus is shared by all the controllers as well as by the CPU, it is, by necessity, a half-duplex bus; i.e., only one operation can occur at any time. The direction of all information transfers on the I/O bus is defined relative to the computer. "Output" always refers to moving information from the computer to a controller; "input" always refers to moving information from a controller to the computer.

## TYPES OF INFORMATION

The information transferred between a computer and a controller can be classified into three types: status, control, and data. Status information tells the computer about the state of the peripheral: is it busy?, is it ready?, is it operating properly? Control information is transferred by the computer to the controller to tell the peripheral what to do. Data is the information which originates from, or is sent to, the device during reading, writing, storing, or processing.

Irrespective of the type of information transferred, is the amount of information transferred. A single bit may be transferred; a collection of bits forming a byte (or character), 16 bits forming a word, or a group of words forming a block may be transferred.

## TYPES OF INFORMATION TRANSFER

Information can be transferred between the computer and a peripheral in one of two ways: under direct program control or under data channel control. An information transfer occurring under direct program control moves a word or part of a word between an accumulator in the CPU and a register in the controller. This type of transfer occurs when an appropriate I/O instruction is executed in the program. An information transfer under data channel control generally moves a block of data, one word at a time, between the computer's memory and the device, through a register in the controller. The block of data is transferred automatically via the data channel once the program, using I/O instructions, sets up the transfer for a particular peripheral.

#### **Direct Program Control**

Direct program control of information transfers, also called "programmed I/O", is a way of transferring single words or parts of words to or from peripherals. Among the peripherals which transfer data in this way are terminals, paper tape readers and punches, card readers, line printers and plotters. Since the data moves through an accumulator, it is readily available to the program for manipulation or decision making. In the case of input, for example, the program can decide whether to read another word or character based on the value of the word or character just read.

However, because at least one instruction--and most likely several since the information must be stored in memory--must be executed for each character or word transferred, direct program control can be efficient only for peripherals which do not have to transfer large quantities of information quickly.

### **Data Channel Control**

Some peripherals, such as discs and magnetic tape transports, are used to transfer large blocks of data. In order to reduce the amount of program overhead required, these blocks are transferred under data channel control. The commands used to set up the data channel transfer are assembled in an accumulator and are transferred to the controller under direct program control. The block of data is then automatically transferred directly between memory and the controller via the data channel. Once the data channel transfer for a block of data has been set up and initiated by the program, no further action by the program is required to complete the transfer. The program can proceed with other tasks while the block transfer is taking place. Each time the controller is ready to transfer a word from the block it requests direct access to memory. When access is granted, the word is transferred. Because several instructions do not have to be executed for each word transferred, block transfers can occur at high rates, in some cases at more than a million words per second.

Since the actual transfer of a word via the data channel could conflict with the program instructions being executed, the program pauses during the transfer of each word. This pause is transparent to the programmer with the exception that the time required for program execution is lengthened.

## PROGRAM INTERRUPT FACILITY

When transferring information under either direct program control or data channel control, the program must be able to determine when the transfer is complete, so that it can start a new transfer or proceed with a task that was dependent on the transfer just completed. Peripherals have status flags which can provide the program with this needed information. The I/O instruction set allows the program to check the status of these flags and perform decisions based on the results of the checks. However, these status checks are timeconsuming, so, to avoid the necessity of continually performing such tests, all DGC computers incorporate a program interrupt facility.

The program interrupt facility provides a peripheral with a convenient means of notifying the processor that it requires service by the program. This is accomplished by allowing the peripherals to interrupt normal program flow on a priority basis. When a peripheral completes an operation or encounters a situation requiring processor intervention, it can request a program interrupt of the processor. The processor honors such a request by interrupting the program in process, saving the address where the interruption occurred, and transferring control to the interrupt handling routine. The interrupt handling routine can identify which peripheral requires service and transfer control to the service routine for that peripheral. After servicing that peripheral, the routine can restore the system to the state it was in when the interrupt occurred.

For computer systems which require large amounts of I/O to many devices, a multi-level priority structure up to 16 levels deep can be established. This structure can be set up to provide rapid service to those devices which are crucial to the efficient operation of the computer system; the less critical devices are serviced in as efficient a manner as possible. The priority interrupt structure, like the rest of the program interrupt facility, is under direct control of the program.

### SUMMARY

The following sections of this Introduction to I/O Programming cover, in detail, the concepts introduced above. The instructions needed to perform a direct program controlled transfer are discussed in terms of their interaction with the controller and the CPU. The mechanics of the program interrupt facility together with methods used to arrange a priority structure are presented. Methods used in performing block transfers via the data channel are followed by a general discussion of the timing concepts which should be considered when designing an efficient system for handling I/O. Finally, examples are presented which illustrate the procedures discussed in this Introduction to I/O Programming.

# I/O INSTRUCTION SET

### INTRODUCTION

Information transfers between the computer and the various peripherals are governed by the program with eight instructions which constitute the I/O instruction set. These instructions allow the program to communicate with the peripherals' controllers and to control the program interrupt facility. This manual covers only those I/O instructions used for these purposes; additional I/O instructions used for special processor functions and options are fully described in the Programmer's Reference Manuals for the ECLIPSE<sup>TM</sup> and NOVA<sup>®</sup> line computers.

The effects of specific I/O instructions necessarily depend on the peripherals to which they are addressed. However, the general functions provided by the I/O instructions (loading and reading registers, issuing control signals, and testing flags) are the same for all peripherals; different peripherals merely use the available functions in different ways. In order to understand the general functions performed by the I/O instructions and how these functions are typically used by peripheral controllers, some knowledge of the architecture of a peripheral controller is required.

### THE TYPICAL CONTROLLER

From the point of view of the program, a peripheral controller operates as a collection of information registers, control registers, and status flags, with which communications are established. With these registers and flags, the program can route data between the computer and the device and monitor the operation of the device. Information registers act as temporary depositories for information being transferred between the computer and the device. For an input operation, the device places information in a register in the controller and the computer then reads the register's contents. For an output operation, the computer places information in a register in the controller and the device can access that information when necessary. Control registers are loaded by the program and are used to control the operation of the device. Status flags are set by the peripheral to reflect its current operating conditions. The program, through the use of I/O instructions can examine these status flags and can alter some of them to change the operating state of the peripheral.

The distinction made here between registers and flags is generally one of information content. A flag contains a single bit of information, while a register is made up of a number of bits. Groups of contiguous bits in a register which convey a single "piece" of information are referred to as "fields". For example, in one of the magnetic tape controller's registers, bits 13-15 act together as a control field to select one of the eight possible tape transports in the subsystem.

The paragraphs below describe only the basic components of a typical controller. The additional structure required for a peripheral using the program interrupt facility or the data channel is discussed in the sections describing those facilities. What follows is meant only to typify the workings of a controller; controllers are tailored to the specific devices they control, so that not all fit the model given here.

#### **Information Registers**

A controller usually contains one or more information registers. Using I/O instructions, the program can load data and control information into these registers from the processor's accumulators and can read data and status information into the accumulators from them. The three types of information considered here--data, control, and status--give rise to three basic types of information registers, which are described below.

#### **Data Registers**

A data register (or data buffer) is used to store data in the controller as it passes between the device and the computer. This buffer is needed because the computer and the device usually operate at different speeds. Since the operation of nearly all peripherals involve the transfer of a word or part of a word of data between the computer and the device, nearly all peripherals controllers contain a data buffer. In the case of peripherals which transfer data under direct program control, the data buffer is directly accessible to the program. Data is transferred between the register in the controller and an accumulator in the central processor by an I/O instruction. In the case of a peripheral which transfers data under data channel control, the data is transferred directly between the register in the controller and memory. Data buffers in the controllers which use the data channel need not be -- and usually are not -accessible to the program.

#### **Control Registers**

Control registers allow the program to supply the controller with information necessary for the operation of the device, such as drive or transport numbers, data block sizes, and command specification. A unit of control information is called a "control parameter". Control parameters typically allow the program to select one of a number of peripheral units in a subsystem, the operation to be performed, and the initial values for flags and counters in the controller. The program specifies control parameters to the controller with an I/O instruction wherein the desired parameters are coded into the appropriate fields of the accumulator used in the transfer.

#### **Status Registers**

Status registers are used to indicate to the program the detailed state of the peripheral. They consist primarily of status flags, but can also contain control parameters. The control parameters contained in status registers are commonly those which change during the operation of the peripheral, and are therefore of importance to the program which must check on the progress of the peripheral's operation. For example, a program transferring consecutive sectors of information on a disc in a single operation can read the current sector address and sector count during the operation in order to determine how far the operation is from completion. Status flags are set by the controller to indicate error conditions or to notify the computer of the basic state of the peripheral.

The classification of controller registers into the three types described above can only be a general one. A register may contain more than one type of information. The most common case of this occurrence is a register that serves as a control register when loaded by the program and as a status register when read by the program. The disc address/sector counter register mentioned in the preceding paragraph is an example of such a combined control and status register.

#### Busy and Done Flags

The Busy and Done flags are the two fundamental flags in a controller and they serve a dual purpose. Together they denote the basic state of the peripheral and can be tested by the program to determine that state. In addition, the program can manipulate these flags in order to control the operation of the peripheral. To place the peripheral in operation, the program sets the Busy flag to 1. The Busy flag remains in this state for the duration of the operation, indicating that the peripheral is in use and should not be disturbed by the program. When the peripheral completes its operation, the controller sets the Busy flag to 0 and the Done flag to 1 to indicate this fact. The setting of the Done flag to 1 can be used to trigger a program interrupt. Whether a program interrupt occurs depends on the state of the interrupt facility. However, no matter what state the interrupt facility is in, no interrupt can occur for that peripheral until its Done flag is set to 1. Therefore, the setting to 1 of the Done flag is defined to "initiate a program interrupt request". At this point, the program can either start the next operation by setting the Done flag to 0 and the Busy flag to 1, or it can idle (clear) the peripheral by setting both flags to 0

#### Other Status Flags

For a relatively simple peripheral, the Busy and Done flags alone may furnish enough status information to allow the program to service the peripheral adequately. However, a more complex peripheral will generally require additional status flags to specify its internal operating conditions more completely to the program. The difference between these additional status flags and the Busy and Done flags lies in the way the program tests them. The program can test the Busy and Done flags directly with a single I/O instruction, but checking any other status flag requires that its value first be read into an accumulator from the status register. Each status flag is assigned by the controller to one of the 16 available bit positions in the status register. The program may the perform any test it requires on the status word after it is read.

#### **Error Flags**

Status flags which indicate errors or malfunctions in the operation of a peripheral are termed "error flags". Two types of error flags can be characterized, according to their effect on the operation of the peripheral when they are set. The first, or passive, type is merely set by the controller in the course of the operation when the associated error occurs. No immediate indication of this type of error is given to the program, and the operation is allowed to continue to completion. The second, or active, type of error flag is set by the controller when the program attempts to start an operation which is not allowed. In this case, the operation never begins and the Done flag is set to 1 immediately to notify the program. This type of error flag is used to prevent a severe and probably irrecoverable error from occurring. In either case, the program must respond, error or not, when it notices that a peripheral is "done". It need only check the appropriate error flag or flags before assuming that the operation it initiated was satisfactorily completed.

For example, among its many status flags, the controller for magnetic tape transports contains error flags to indicate parity errors and illegal operations. During a read operation, when a character is read with incorrect parity, the Parity Error flag is set to 1. No immediate notification of the error is given to the program and the read operation is allowed to finish. The parity error can be detected at the completion of the operation, when the program should check for errors. At this time appropriate action can be taken, such as trying to read the misread section of tape again or printing an error message on the console terminal. The Illegal flag, on the other hand, which is set when an illegal operation is attempted, prevents the operation from starting. The controller immediately sets both the Done and Illegal flags to 1 to notify the program. Illegal operations for a magnetic tape transport include writing on a tape that is write-protected and spacing backwards when the tape is at the beginning of tape marker.

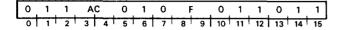

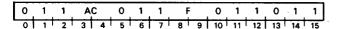

### INSTRUCTION FORMAT

The general format of the I/O instructions is shown below.

| 0 | 1 | 1 | A | с | OF | col | ΡE | CONT | ROL |    | DE | VICE | COD | E  |    |

|---|---|---|---|---|----|-----|----|------|-----|----|----|------|-----|----|----|

| 0 |   | 2 | 3 | 4 | 5  | 6   | 7  | 8    | 9   | 10 | 11 | 12   | 13  | 14 | 15 |

Bits 0-2 are 011 and identify this as an I/O instruction, bits 3-4 specify an accumulator, bits 5-7 contain the operation code, bits 8-9 specify a flag control function or test condition, and bits 10-15 specify the code of the device.

#### **Device Code Field**

Bits 10-15 in an I/O instruction select the peripheral that is to respond to the instruction. The instruction format thus allows for 64 device codes, numbered  $0-77_8$ . In all computers, device code 0 is not assigned to any peripheral, and device code 778 is used to implement a number of specific processor functions, such as reading the console switches and controlling the program interrupt facility. Depending on the computer, a number of other specific device codes are reserved for processor options or features. The remaining device codes are available for referencing peripherals. Many of these codes have been assigned by Data General Corporation to standard peripherals, and the assembler recognizes convenient mnemonics for these codes. The list of the standard device code assignments and their associated mnemonics is given in Appendix A.

#### **Flag Control Field**

The Busy and Done flags are either manipulated or tested by the control functions or test conditions specified in bits 8 and 9 of the I/O instructions. In those instructions which allow flag manipulation, bits 8 and 9 are referred to as the F field. The flag control commands available, along with the associated mnemonics and bit configurations and the functions typically performed, are as follows:

| F field | Command | Mnemonic  | Control Function                                                                                                  |

|---------|---------|-----------|-------------------------------------------------------------------------------------------------------------------|

| 00      | (none)  | (omitted) | None                                                                                                              |

| 01      | Start   | S         | Start the periph-<br>eral by setting the<br>Busy flag to 1 and<br>the Done flag to 0.                             |

| 10      | Clear   | С         | Clear (idle) the<br>peripheral by set-<br>ting both the Busy<br>and Done flags to<br>0.                           |

| 11      | Pulse   | Р         | Pulse the control-<br>ler to achieve a<br>special effect.<br>The effect, if any,<br>depends on the<br>peripheral. |

In the I/O instruction which allows flag testing, bits 8 and 9 are referred to as the T field. The bit configurations, mnemonics, and test conditions they select are as follows:

| T field | Mnemonic      | Next instruction is skipped if: |

|---------|---------------|---------------------------------|

| 00      | BN            | Busy flag is 1 (Non-zero)       |

| 01      | $\mathbf{BZ}$ | Busy flag is 0 (Zero)           |

| 10      | DN            | Done flag is 1 (Non-zero)       |

| 11      | DZ            | Done flag is 0 (Zero)           |

Two important features of the I/O instruction set result from the nature of the flag control field. First, because the flag control field is separate from the operation code field, a single I/O instruction can both transfer information between the controller and the computer and simultaneously control the operation of the peripheral. Secondly, the use of the flag control field as a T field allows the direct testing of a controller's Busy or Done flag in a single instruction, so that quick decisions based on the basic state of the peripheral can be made by the program.

### **Operation Code Field**

The 3-bit operation code field selects one of the eight I/O instructions. In two of these instructions, no information transfer is specified; instead, bits 8 and 9 may specify either a control function or a flag test condition as described above. The remaining six instructions involve an information transfer between the computer and the designated peripheral controller and may also specify a control function to be performed after the information transfer has been completed. The program can, therefore, access up to six registers in any one controller. Up to three of these six registers are output registers which can be loaded by the program with either data or control information. The other three are input registers, from which the program can read either data or status information. It is entirely possible and, in fact, quite common for two different I/O instructions, one input and one output, to reference the same register in a controller. However, this is not in any way required by the nature of the I/O instruction set; potentially six different registers in a controller may be accessible to the program.

In order to give names and mnemonics to the I/O instructions in their general form, the registers in a peripheral controller which are accessible to the program are referred to with letter designations. The three input registers are called the "A input buffer", the "B input buffer", and the "C input buffer". Similarly, the three output registers are

called the "A output buffer", the "B output buffer", and the "C output buffer". Thus, for example, to read data from a peripheral controller's A input buffer, a DATA IN A instruction, with mnemonic DIA, is issued to that peripheral.

The eight operation codes, their associated mnemonics, and the instructions specified are as follows:

| Operation Code |          |                                                                                                 |

|----------------|----------|-------------------------------------------------------------------------------------------------|

| field          | Mnemonic | Instruction                                                                                     |

| 000            | NIO      | No Input or Output<br>but perform the flag<br>control function<br>specified.                    |

| 001            | DIA      | Read Data Into the computer from the $\underline{A}$ input buffer.                              |

| 010            | DOA      | Write Data Out from<br>the computer to the A<br>output buffer.                                  |

| 011            | DIB      | Read Data Into the computer from the $\underline{B}$ input buffer.                              |

| 100            | DOB      | Write Data Out from<br>the computer to the<br><u>B</u> output buffer.                           |

| 101            | DIC      | Read Data Into the computer from the $\underline{C}$ input buffer.                              |

| 110            | DOC      | Write Data Out from<br>the computer to the<br><u>C</u> output buffer.                           |

| 111            | SKP      | SKiP the next in-<br>struction if the test<br>selected for the<br>Busy or Done flag<br>is true. |

#### **Accumulator Field**

Bits 3 and 4 in an I/O instruction select one of the central processor's four accumulators: AC0, AC1, AC2, or AC3. In those instructions which involve an information transfer between the processor and a peripheral controller, the specified accumulator either furnishes the information for an output transfer or receives the information in an input transfer. In the two I/O instructions which do not involve an information transfer, the accumulator field is ignored. The assembler sets bits 3 and 4 in these instructions to 0; however, any bit combination will do, and no accumulator will ever be affected by these two instructions.

#### INSTRUCTIONS

A number of abbreviations and symbols are used in this manual to aid in defining how an instruction may be coded in assembly language. Abbreviations used are as follows:\*

| AC or ac | accumulator             |

|----------|-------------------------|

| F or f   | flag control command    |

| T or t   | flag test command       |

| device   | device code or mnemonic |

The following symbols are not coded, rather they perform these functions:

- <br/>

<br/>

Indicates an optional operand. The operand enclosed in the brackets (e.g., <<br/>  $(\underline{f}>)$  may be coded or not, depending on whether the associated option is desired.

- Indicates a specific substitution is required. Substitute the desired number, letter or letters, or symbol from the class, as defined by the abbreviation for which the substitution is being made. For example, "<u>ac</u>" indicates that an accumulator specifier is required. To select AC2, code either a "2" or a symbol whose value is 2.

When describing the format of a word involved in an information transfer between the computer and a controller, the various fields and bits in the word are labeled with names descriptive of their functions. Bits in the word which are not used by the controller are shaded. Shaded bits are ignored on output and set to 0 on input.

#### **NO I/O TRANSFER**

| ] | NIC | )< <u>f</u> | >   | der | vice | 9 |   |   |   |   |    |    |      |    |    |    |

|---|-----|-------------|-----|-----|------|---|---|---|---|---|----|----|------|----|----|----|

|   | 0   | , 1         | , I | Α   | c    | 0 | 0 | 0 |   | F |    | DE | /ICE | co | DE |    |

|   | 0   | 1           | 2   | 3   | 4    | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13 | 14 | 15 |

The Busy and Done flags in the controller of the specified device are set according to the function specified by F. When the assembler encounters the mnemonic NIO, it sets the AC field bits to 0. However, these bits are ignored and may have any value. The contents of all the accumulators are unchanged.

#### I/O SKIP

SKP < t > device

| 0 | I | 1 | А | C | 1 | 1 | ļ |   | ŗ |    | DEV | /ICE | COL | )E |    |

|---|---|---|---|---|---|---|---|---|---|----|-----|------|-----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11  | 12   | 13  | 14 | 15 |

Skip the next sequential instruction if the test condition specified by T is true for the specified controller. When the assembler encounters the mnemonic SKP<t>, it sets the AC field bits to 0. However, these bits are ignored and may have any value. The contents of all the accumulators and the Busy and Done flags for the specified device remain unchanged.

#### DATA IN A

| DIA <f></f> | ac, device |

|-------------|------------|

|             |            |

| 0 | I, | 1 | Α | С | 0 | 0 | 1 |   | F |    | DE\ | /ICE | co | DE |    |

|---|----|---|---|---|---|---|---|---|---|----|-----|------|----|----|----|

| 0 | 1  | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11  | 12   | 13 | 14 | 15 |

The contents of the A input buffer in the specified controller are placed in the specified AC. After the data transfer, the controller's Busy and Done flags are set according to the function specified by **F**. The number of information bits transferred depends on the size of the buffer and the mode of operation of the peripheral. Bits in the specified AC that do not receive information are set to 0.

#### DATA OUT A

| $DOA < \underline{f} >$ | <u>ac</u> , <u>device</u> |

|-------------------------|---------------------------|

|-------------------------|---------------------------|

| 0 | 1 |   | А | С | 0 | l | 0 |   | F |    | DE \ | /ICE | cot |    |    |

|---|---|---|---|---|---|---|---|---|---|----|------|------|-----|----|----|

| 0 |   | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11   | 12   | 13  | 14 | 15 |

The contents of the specified AC are placed into the A output buffer in the specified controller. After the data transfer, the controller's Busy and Done flags are set according to the function specified by **F**. The number of information bits loaded into the buffer depends on the size of the buffer and the mode of operation of the peripheral. Any unused bits are ignored by the controller. The contents of the specified AC remain unchanged.

New coding aids have been incorporated in some updated portions of this manual. Where the newer aids are used, the text specifically refers the reader to Appendix E, where they are described.

#### $DIB < \underline{f} > \underline{ac}, \underline{device}$

| 0 | 1 | 1 | Д | C | 0 | , 1 | 1 |   | F |      | DEV | ICE | COD | Ξ  |    |

|---|---|---|---|---|---|-----|---|---|---|------|-----|-----|-----|----|----|

| 0 | ' | 2 | 3 | 4 | 5 | 6   | 7 | 8 | 9 | ' 10 | 11  | 12  | 13  | 14 | 15 |

The contents of the B input buffer in the specified controller are placed in the specified AC. After the data transfer, the controller's Busy and Done flags are set according to the function specified by  $F_{\circ}$ . The number of information bits transferred depends on the size of the buffer and the mode of operation of the peripheral. Bits in the AC that do not receive information are set to  $0_{\circ}$ .

#### DATA OUT B

DOB < f > ac, device

| Ο | ) | 1 | 1 | Α | <u>c</u> | 1 | 0 | 0 |   | F |    | DEV | /ICE | cot | ρE |    |

|---|---|---|---|---|----------|---|---|---|---|---|----|-----|------|-----|----|----|

| 0 | 5 | 1 | 2 | 3 | 4        | 5 | 6 | 7 | 8 | 9 | 10 | 11  | 12   | 13  | 14 | 15 |

The contents of the specified AC are placed in the B output buffer in the specified controller. After the data transfer, the controller's Busy and Done flags are set according to the function specified by F. The number of information bits loaded into the buffer depends on the size of the buffer and the mode of operation of the peripheral. Any unused bits are ignored by the controller. The contents of the specified AC remain unchanged.

#### DATA IN C

| $\mathrm{DIC} < \mathbf{\underline{f}} >$ | ac, device |

|-------------------------------------------|------------|

|-------------------------------------------|------------|

| 0 | 1 | ١ | Α | С | 1 | 0 | I |   | F |    | DE١ |    | со | DE |    |

|---|---|---|---|---|---|---|---|---|---|----|-----|----|----|----|----|

| 0 | I | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 01 | 11  | 12 | 13 | 14 | 15 |

The contents of the C input buffer in the specified controller are placed in the specified AC. After the data transfer, the controller's Busy and Done flags are set according to the function specified by F. The number of information bits transferred depends on the size of the buffer and the mode of operation of the peripheral. Bits in the AC that do not receive information are set to 0.

### DATA OUT C

$DOC < \underline{f} > \underline{ac}, \underline{device}$

|   |   |   | = |   | : _ = |   | _ |   |   |   |    |    |      |     |    |    |

|---|---|---|---|---|-------|---|---|---|---|---|----|----|------|-----|----|----|

| Γ | 0 | I | 1 | A | C     |   | 1 | 0 |   | F |    | DE | VICE | COI | DE |    |

|   | 0 | 1 | 2 | 3 | 4     | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12   | 13  | 14 | 15 |

The contents of the specified AC are placed in the C output buffer of the specified controller. After the data transfer, the controller's Busy and Done flags are set according to the function specified by F. The number of information bits loaded into the buffer depends on the size of the buffer and the mode of operation of the peripheral. Any unused bits are ignored by the controller. The contents of the specified AC remain unchanged.

The single letter mnemonic for the desired control command is appended to the basic mnemonic. An NIO instruction alone with any device code is a "no-op" (that is, it has no effect). To place the high speed paper tape reader in operation, an NIOS 12, or, using the reader's mnemonic, an NIOS PTR instruction could be executed. Both of these instructions assemble as  $060112_8$ (0 110 000 001 001 010) and cause the reader to rea one character from the tape into the controller's data buffer.

To determine when the character is in the buffer without using the program interrupt we can wait for either the Busy flag to be set to 0 or the Done flag to be set to 1. For example, giving

#### SKPDN PTR

JMP .-1

keeps the processor from proceeding until the reader controller has set the Done flag to 1.

Once the character has been loaded into the data buffer, the Done flag is set to 1 and the processor will continue. The character can be read into the right half of AC2 by giving

#### DIA 2, PTR

If another character is to be read the transfer can be made with a

#### DIAS 2, PTR

which brings the character into AC2, sets the Done flag to 0, the Busy flag to 1, and causes the reader to read the next character. If the data buffer contains the final character to be read from tape, giving

#### DIAC 2, PTR

retrieves the character and sets both the Busy and Done flags to 0, thus idling the reader.

In the remainder of this manual the discussion of each peripheral treats only the control functions and the applicable I/O transfer instructions. The skips apply to all and are the same in all cases. Giving a data-in instruction that does not apply to a peripheral (either because the peripheral is output-only or does not have the buffer specified) sets all bits of the addressed accumulator to 0 but the specified flag control function is carried out. Similarly, a data-out instruction that does not apply is a no-op except for the specified control functions. When the device code is undefined or the addressed peripheral is not in the system, any data-out or NIO instruction, a SKPBN, or a SKPDN is a no-op; a SKPBZ or SKPDZ is an unconditional skip (equivalent to a JMP .+2); and any data-in instruction simply sets all bits of the specified AC to 0.

۴

# **PROGRAM INTERRUPT FACILITY**

#### INTRODUCTION

When a peripheral completes an operation, the controller sets its Done flag to 1 to indicate that program service is required. The program can test the state of the Done flag repeatedly with I/O SKIP instructions to determine when this occurs. However, continual interrogation of the Done flag by the program is generally wasteful of computing time, especially when flag checks need to be done frequently in order to ensure that service is not delayed so long that the peripheral loses data. The program interrupt facility provides a peripheral with a convenient means of notifying the processor that service is required.

All peripherals which use the program interrupt facility have access to a single direct line to the processor, called the Interrupt Request Line, along which their requests for service are communicated. An interrupt request can be generated by a peripheral when the peripheral's Done flag is set to 1. The processor can respond to, or "honor", an interrupt request by interrupting the normal flow of program execution and transferring control to an interrupt handling routine. The programmer can control which peripherals may request interrupts and when the processor may start an interrupt, by manipulating a number of flags which are distributed among the processor and the peripherals.

The operation of the program interrupt facility, as controlled by these flags, is described below. Following portions of this section detail the instructions used to control the program interrupt facility, describe the implementation of a priority interrupt scheme, offer further suggestions for programming an interrupt handler, and explain the operation of the vector instruction, which allows the ECLIPSE computer to automatically perform much of its interrupt processing.

### OPERATION

#### **Control Flags**

The operation of the program interrupt facility is governed by the Interrupt On (ION) flag in the central processor and by the Done and Interrupt Disable flags in each peripheral which uses the facility. By manipulating these flags, the program can choose to disregard interrupt requests altogether, or it can selectively ignore certain peripherals.

#### Interrupt On Flag

The major control flag for the program interrupt facility is the Interrupt On flag in the central processor. To enable the interrupt facility the program sets ION to 1, allowing the processor to respond to interrupt requests transmitted to it along the Interrupt Request Line. Setting ION to 0 disables the entire interrupt facility, causing the processor to ignore all interrupt requests.

The Interrupt On flag is manipulated by the program exactly like a Busy flag for the central processor. A Start command in any I/O instruction directed to the CPU (device code  $77_8$ ) sets ION to 1, a Clear command in such an instruction sets ION to 0. (ION is also set to 0 at power-up and when the RESET console switch is pressed.)

### Interrupt Disable Flags

The controller for each peripheral which uses the program interrupt facility contains an Interrupt Disable flag which allows the program to disable interrupts from that peripheral. When a peripheral's Interrupt Disable flag is set to 1, the peripheral is prevented from making an interrupt request.

The Interrupt Disable flags of all peripherals are manipulated at once with a single I/O instruction. This instruction, MASK OUT (MSKO), sets up the Interrupt Disable flags of all peripherals connected to the program interrupt facility according to a mask contained in the accumulator specified by the instruction. Each peripheral is assigned by its hardware to a bit position in the mask. (Mask bit assignments for standard peripherals are given in Appendix A.) When a MASK OUT instruction is given, each peripheral's Interrupt Disable flag is set to the value of the assigned bit of the mask. Also, at power-up and when the RESET console switch is pressed, all Interrupt Disable flags are set to 0.

#### **Interrupt Requests**

Interrupt requests by a peripheral are governed by its Done and Interrupt Disable flags. When a peripheral completes an operation, it sets its Done flag to 1, and this action initiates a program interrupt request. If its Interrupt Disable flag is 0, the request is communicated to the CPU. If the Interrupt Disable flag is 1, the request is not communicated to the CPU; it is blocked until the Interrupt Disable flag is set back to 0. If the ION flag is 1, the processor has to honor the interrupt request as soon as it is able.

The processor is able to interrupt the sequential flow of program instructions if all of the following conditions hold:

1. The processor has just completed an instruction or a data channel transfer occurring between two instructions.

- 2. At least one peripheral is requesting an interrupt.

- 3. Interrupts are enabled; that is, ION is 1.

- 4. No peripheral is waiting for a data channel transfer; that is, there are no outstanding data channel requests. The data channel has priority over program interrupts.

When the processor finishes an instruction it takes care of all data channel requests before it starts an interrupt; this includes any additional data channel requests that are initiated while data channel transfers are being made. When no more peripherals are waiting for data channel transfers, the processor starts an interrupt if ION is 1 and at least one peripheral is requesting an interrupt.

#### **Processor Response**

The processor starts an interrupt by automatically executing the following sequence:

- 1. It sets ION to 0 so that no further interrupts may be started.

- 2. It stores the contents of the program counter (which point to the next instruction in the interrupted program) in location 0, so that a return to the interrupted program can be made after the interrupt service routine has finished.

- 3. It simulates a JMP@1 instruction to transfer control to the interrupt service routine. Location 1 should contain the address of the routine or the first part of an indirect address chain that points to the routine.

#### Servicing An Interrupt

The interrupt service routine (or handler) should save the state of the processor, identify which peripheral requires service, and service the peripheral.

Saving the state of the processor involves saving the contents of any accumulators that will be used in the interrupt service routine and saving the carry bit if it will be used. The state of the processor must be saved so that it may be restored before the interrupted program is allowed to resume.

### **Peripheral Identification**

There are three ways in which the interrupt handler can identify which peripheral requires service.

- 1. On the NOVA and ECLIPSE lines of computers, the interrupt handler can execute a polling routine. This routine is merely a sequence of I/O SKIP instructions which test the states of the Done flags of all peripherals in use. With this method peripheral priorities are determined by the order in which the tests are performed. Note that the polling technique disregards the state of the Interrupt Disable flags. Peripherals which are masked out will be recognized if their Done flags are 1, even though these peripherals could not have caused the interrupt.

- 2. On the NOVA and ECLIPSE lines of computers, the interrupt handler can issue an INTERRUPT ACKNOWLEDGE instruction (INTA). This instruction reads the device code of the first peripheral on the I/O bus that is requesting an interrupt, into a specified accumulator. Note that with this method the Interrupt Disable flags are significant. Peripherals which are masked out cannot request an interrupt and, therefore, cannot respond to the INTERRUPT ACKNOWL-EDGE instruction.

- 3. On the ECLIPSE line of computers the interrupt handler can issue a VECTOR instruction (VCT). This instruction determines which peripheral requires service in exactly the same way as the INTERRUPT ACKNOWLEDGE instruction. However, the device code obtained is not placed in an accumulator but is used as an index into a table of addresses. Besides vectoring automatically to the correct peripheral service routine, the VECTOR instruction can optionally switch stack contexts, save the state of the processor, and establish a new priority level. Because the VECTOR instruction is available only on the ECLIPSE computer, and because its operation is relatively complex, it is described later in a section of its own.

#### **Peripheral Service Routine**

After determining which peripheral requires service, the interrupt handler generally transfers control to a peripheral service routine. This routine performs the information transfer to or from that peripheral (if required) and either starts the peripheral on a new operation or idles the peripheral if no more operations are to be performed at this time.

#### **Dismissing An Interrupt**

When all service for the peripheral has been completed, either the peripheral service routine or the main interrupt handler should perform the following sequence to dismiss the interrupt.

- 1. Set the peripheral's Done flag to 0 to dismiss the interrupt request which was just honored. If this is not done, the undismissed interrupt request will cause another interrupt--this time incorrectly--as soon as the interrupt handler finishes and attempts to return control to the interrupted program.

- 2. Restore the pre-interrupt states of the accumulators and the carry bit.

- 3. Set the Interrupt On flag to 1 to enable interrupts again.

- 4. Jump back to the interrupted program. (Usually a JMP@0 instruction is given.)

The instruction that enables interrupts (usually INTEN) sets the Interrupt On flag to 1, but the processor does not recognize that the state of the ION flag has changed to 1 until the next instruction begins. Thus, after the instruction that turns interrupts back on, the processor always executes one more instruction (assumed to be the return to the interrupted program) before another interrupt can start. The program must give this final return instruction immediately after enabling interrupts in order to ensure that no waiting interrupt can overwrite the contents of location 0 before they are used to return control to the interrupted program.

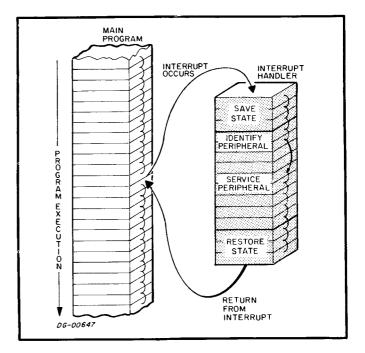

The following diagram shows how normal program flow is altered during a program interrupt. The interrupt handler is shaded to indicate that this block of instructions is not interruptable since the processor sets the ION flag to 0 to disable further interrupts when the interrupt occurred. Interrupts are not enabled again until the interrupt handler executes its INTERRUPT ENABLE instruction just prior to returning control to the interrupted program.

### INSTRUCTIONS

The instructions which control the program interrupt facility use special device code  $77_8$ (mnemonic CPU). When this device code is used, bits 8 and 9 of the skip instructions test the state of the Interrupt On flag; in the other instructions these bits turn interrupts on or off by setting ION to 1 (Start command) or 0 (Clear command).

#### **INTERRUPT ENABLE**

INTEN

#### NIOS CPU

| 0 | 1, | I | A | c   | 0 | 0 | 0 | 0 | 1 | 1  | 1  | 1  | 1  | 1  | I  |

|---|----|---|---|-----|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1  | 2 | 3 | ' 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Set the Interrupt On flag to 1 to allow the processor to respond to interrupt requests. If the Interrupt On flag actually changes state (from 0 to 1), the processor will execute one more instruction before it can start an interrupt. On the ECLIPSE computer, the processor will execute one more instruction before starting an interrupt even if the Interrupt On flag was already 1. However, if that instruction is one of those that is interruptable, then an interrupt can occur as soon as the instruction begins to execute. The assembler recognizes the mnemonic INTEN as equivalent to NIOS CPU.

#### **INTERRUPT DISABLE**

INTDS

#### NIOC CPU

| 0 | 1 | 1 | Д | C | 0 | ,0 | 0   | I | 0 | 1  | 1  | , 1 |    | 1  | 1  |

|---|---|---|---|---|---|----|-----|---|---|----|----|-----|----|----|----|

| 0 | I | 2 | 3 | 4 | 5 | 6  | ' 7 | 8 | 9 | 10 | 11 | 12  | 13 | 14 | 15 |

Set the Interrupt On flag to 0 to prevent the processor from responding to interrupt requests. The assembler recognizes the mnemonic INTDS as equivalent to NIOC CPU.

#### SKIP IF INTERRUPTS ENABLED

| 0 | I | , ! | Α | с | 1 | , 1 | 1 | 0 | 0 | 1  | ١, | ١  | 1  | 1  |    |

|---|---|-----|---|---|---|-----|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2   | 3 | 4 | 5 | 6   | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Skip the next sequential instruction if the Interrupt On flag is 1.

#### SKIP IF INTERRUPTS DISABLED

SKPBZ CPU

|   | 0 | 1 | 1 | Α | C | 1 | 1 | 1 | 0 | 1 | 1  |   | 1  | 1  | I  |    |

|---|---|---|---|---|---|---|---|---|---|---|----|---|----|----|----|----|

| Ĵ | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | Н | 12 | 13 | 14 | 15 |

Skip the next sequential instruction if the Interrupt On flag is 0.

#### MASK OUT

MSKO ac

| DOB < f > | ac,CPU |

|-----------|--------|

|           |        |

| 0 | , 1      | 1 | А | IC | 1 | 0 | 0 |   | F | 1  | 1 | 1  | 1  | 1  | T  |

|---|----------|---|---|----|---|---|---|---|---|----|---|----|----|----|----|

| 0 | <b>'</b> | 2 | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | П | 12 | 13 | 14 | 15 |

Set the Interrupt Disable flags in all peripherals according to the mask contained in the specified AC. (A 1 in a mask bit sets the flags in all peripherals assigned to that bit to 1, a 0 sets them to 0.) After the Interrupt Disable flags are set, the Interrupt On flag is set according to the function specified by F. The contents of the specified AC remain unchanged. Mask bit assignments for standard peripherals are given in Appendix A. The assembler recognizes the instruction MSKO ac as equivalent to DOB ac, CPU.

#### INTERRUPT ACKNOWLEDGE

INTA ac

| $DIB < \underline{f} >$ | ac, | CPU |

|-------------------------|-----|-----|

|                         |     |     |

| 0 | 1 | I | А | C | 0 | I | 1 |   | - | 1  | I  | 1  | 1  | 1  | 1  |

|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

The device code of that peripheral requesting an interrupt which is closest to the processor along the I/O bus is placed in bits 10-15 of the specified AC. Bits 0-9 are set to 0. After the data transfer, the Interrupt On flag is set according to the function specified by F. If no peripheral is requesting an interrupt, the specified AC is set to 0. The assembler recognizes the instruction INTA ac as equivalent to DIB ac, CPU.

IORST

| DIC | C< <u>f</u> | > | ac | , C1 | PU |   |   |   |   |    |    |    |    |    |    |

|-----|-------------|---|----|------|----|---|---|---|---|----|----|----|----|----|----|

| 0   |             |   | А  | C    | Ι  | 0 | 1 |   | F | I  | 1  | I  |    | 1  | I  |

| 0   |             | 2 | 3  | 4    | 5  | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

Reset all peripherals connected to the I/O bus: set their Busy, Done, and Interrupt Disable flags to 0 and, depending on the peripheral, perform any other required initialization. After the peripherals' flags are altered, the Interrupt On flag is set according to the function specified by F. The assembler recognizes the mnemonic IORST as equivalent to DICC 0, CPU--that is, as the instruction defined here with F set to 10.

If the mnemonic DIC is used to perform this function, an accumulator must be coded to avoid assembly errors. Regardless of how the instruction is coded, during execution the AC field is ignored and the contents of the specified AC remain unchanged. At power-up and when the RESET console switch is pressed, the processor performs the equivalent of an IORST instruction.

The assembler recognizes a number of convenient mnemonics for instructions that control the program interrupt.

| Mnemonic       | Instruction           | Mnemonic<br>Equivalent | Octal<br>Equivalent |  |  |

|----------------|-----------------------|------------------------|---------------------|--|--|

| INTEN          | INTERRUPT ENABLE      | NIOS CPU               | 060177              |  |  |

| INTDS          | INTERRUPT DISABLE     | NIOC CPU               | 060277              |  |  |

| MSKO <u>ac</u> | MASK OUT              | DOB <u>ac</u> ,CPU     | 062077              |  |  |

| INTA <u>ac</u> | INTERRUPT ACKNOWLEDGE | DIB <u>ac</u> ,CPU     | 061477              |  |  |

| IORST          | I/O RESET             | DICC 0,CPU             | 062677              |  |  |

To set up the Interrupt Disable flags according to the mask contained in AC2, give

#### MSKO 2 or DOB 2, CPU

However, there is one important difference between these special mnemonics and the standard ones: mnemonics for enabling and disabling interrupts cannot be appended to them. Thus, to set the Interrupt On flag to 0 while performing a MASK OUT instruction using AC2 give

#### DOBC 2, CPU

Note that use of the mnemonic IORST sets the Interrupt On flag to 0. To set the flag to 1 while resetting the peripherals give

#### DICS 0, CPU

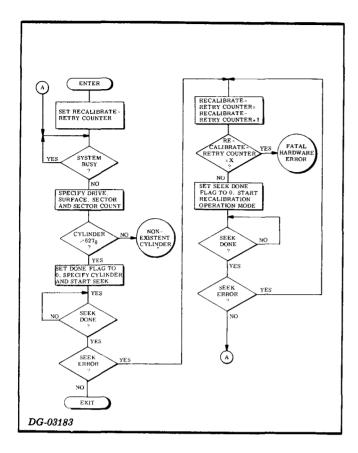

#### PRIORITY INTERRUPTS

If the Interrupt On flag remains 0 throughout the interrupt service routine, the routine cannot be interrupted, and there is only one level of peripheral priority. All peripherals that have not been disabled by the program are, for the most part, equally able to request interrupts and receive interrupt service. Only when two or more peripherals are requesting an interrupt at exactly the same time is a priority distinction made. When this happens, priority is determined either by the order in which I/O SKIP instructions are given or, if the INTERRUPT ACKNOWLEDGE or VECTOR instruction is used, by the order of peripherals along the I/O bus. In a system with peripherals of widely differing speeds and/or service requirements, a more extensive priority structure may be required. The program interrupt facility hardware and instructions allow the program to implement up to 16 interrupt priority levels.

For example, suppose that a card reader and a Teletype<sup>®</sup> are being operated at the same time. While a card is being read, an interrupt is requested as each new column of data is available, and the program must read this data within 430 microseconds, typically, before it is overwritten in the Data Buffer by the data from the next column. If the Teletype service routine takes 300 microseconds, card reader service will never be delayed longer than this, and a single-level program interrupt scheme will suffice. However, this interrupt scheme will not work if the Teletype service routine takes 600 microseconds, since a card reader interrupt request initiated soon after Teletype service is begun will not be honored in time, and a column of data will be lost. In order to avoid losing data, the program interrupt scheme used must allow the card reader to interrupt the lengthy Teletype service routine. This involves creating a two-level priority structure and assigning the card reader to the higher priority level.

In general, a multiple-level priority interrupt scheme is used to allow higher-priority peripherals to interrupt the service routines of lower-priority peripherals. A hierarchy of priority levels can be established through program manipulation of the Interrupt Disable flags of all peripherals in the system. When the interrupt request from a peripheral of a certain priority is honored, the interrupt handler sets up the new priority level by establishing new values for all peripherals' Interrupt Disable flags according to an appropriate "Interrupt Priority Mask" used with the MASK OUT instruction. Peripherals whose Interrupt Disable flags are set to 1 by the corresponding bit of this priority mask are "masked out", or disabled, and are thereby regarded as being of lower priority than the peripheral being serviced. Peripherals which are not masked out assume a higher priority than the

Teletype<sup>®</sup> is a registered trademark of Teletype Corporation, Skokie, Illinois. All references to teletypes in this manual shall apply to this mark.

peripheral being serviced. Before proceeding with the peripheral service routine, the Interrupt On flag is set to 1 so that the higher-priority peripherals may interrupt the current service routine.

### Interrupt Priority Mask

The bit of the priority mask that governs the Interrupt Disable flag for a given peripheral is assigned to that peripheral by the hardware and cannot be changed by the program. Although lower-speed devices are generally assigned to higher-numbered mask bits, no implicit priority ordering is intended. The manner in which these priority levels are ordered is completely up to the programmer. By means of the priority mask the program can establish any desired priority structure, with one limitation: in the cases in which two or more peripherals are assigned to the same bit of the priority mask, these peripherals are constrained to be at the same priority level. When a peripheral causes an interrupt, a decision must be made whether to place all other peripherals which share the same mask bit with the interrupting peripheral at a higher or lower priority level. If a decision is made to mask out all peripherals which share that priority mask bit, the interrupting peripheral is also masked out.

### **Priority Interrupt Handler**

A priority interrupt handler differs from a singlelevel interrupt handler in several ways. The handler must be "re-entrant". This means that if a peripheral service routine is interrupted by another, higher priority peripheral, no information required by the handler to restore the state of the machine, is lost. The two items of information which should be saved, in addition to those saved by a single-level interrupt handler, are the return address (the contents of location 0) and the current priority mask. This information must be stored in different locations each time the interrupt handler is entered at a higher level. Doing this ensures that the necessary return information belonging to an earlier interrupt is not overwritten by a higher level interrupt. A common method of storing return information for a re-entrant interrupt handler is through the use of push-down stacks.

The interrupt handler (including the peripheral service routines) for a multi-level priority scheme should perform the following tasks:

- 1. Save the state of the processor, that is, the contents of the accumulators, the carry bit, location 0, and the current priority mask.

- 2. Identify the peripheral that requested the interrupt.

- 3. Transfer control to the service routine for that peripheral.

- 4. Establish the new priority mask with a MASK OUT instruction for that peripheral's service routine and store it in memory at the location reserved for the current priority mask for that level of interrupt.

- 5. Enable interrupts. Now, any peripheral not masked out can interrupt this service routine.

- 6. Service the peripheral that requested the interrupt.

- 7. Disable interrupts in preparation for dismissal of this interrupt level, so that no interrupts will occur during the transition to the next lower level.

- 8. Restore the state of the processor, including the former contents of the accumulators and the carry bit and reinstitute the pre-interrupt priority mask with a MASK OUT instruction.

- 9. Enable interrupts.

- 10. Transfer control to the return address which was saved from location 0.

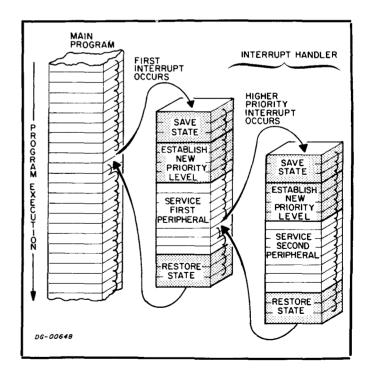

The diagram below is a simplified representation of program flow in a priority interrupt environment. Shaded areas indicate non-interruptable sections of instructions. Additional higherpriority interrupts could increase the depth of interrupts still further.

#### The Vector Instruction

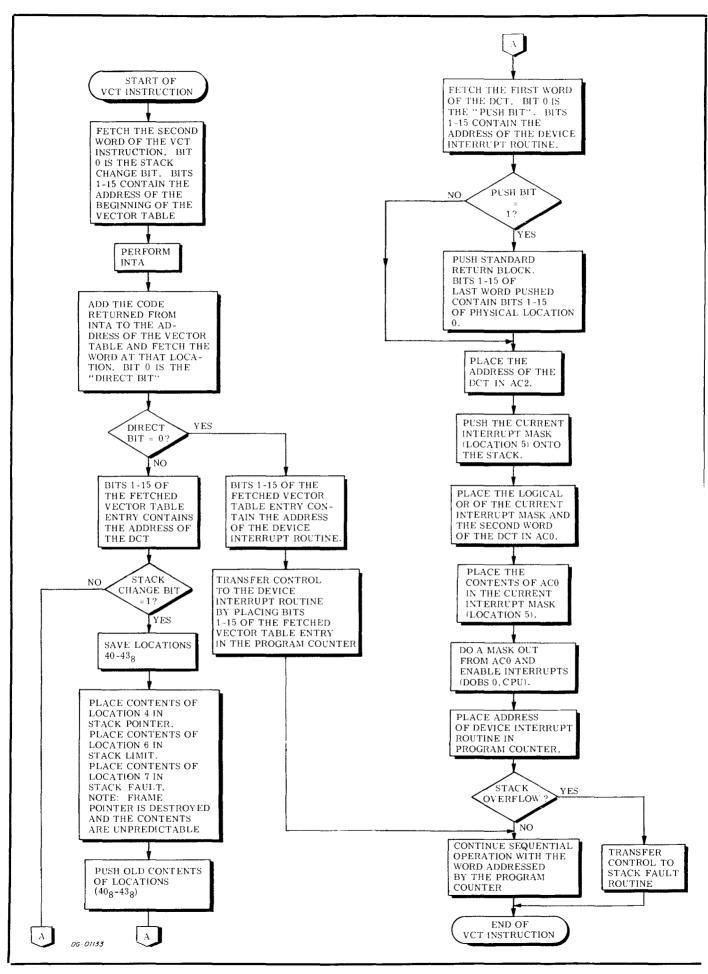

The ECLIPSE line of computers incorporates an instruction which greatly reduces the burden of programming a priority interrupt system. Since this instruction is available only on the ECLIPSE line of computers, it is described separately below. In effect, the VECTOR instruction (VCT) can be used to perform the first five tasks listed above for the multi-level priority interrupt handler.

#### VECTOR ON INTERRUPTING DEVICE CODE

VCT <@>displacement

| - |   |     | - |   |   |     |           |     |     |     |    |    |    |    |    |

|---|---|-----|---|---|---|-----|-----------|-----|-----|-----|----|----|----|----|----|

| 0 | 1 |     | 0 | 0 | 0 |     | <br>_   _ | 1   | . 1 | . 1 | I  | 1  | 1  | 1  | I  |

| 0 | 1 | 2   | 3 | 4 | 5 | 6   | 7         | 8   | 9   | 10  | 11 | 12 | 13 | 14 | 15 |

|   |   |     |   |   |   |     |           | ACE | MEN |     |    |    |    |    |    |

| @ |   | ι I | 1 | . |   | ייו |           |     |     | ,   |    |    |    |    |    |

| 0 | I | 2   | 3 | 4 | 5 | 6   | 7         | 8   | 9   | 10  | 11 | 12 | 13 | 14 | 15 |

This instruction provides a fast and efficient method for transferring control from the main I/O interrupt handler to the correct interrupt service routine for the interrupting device. Bit 0 of the second word of the instruction is the "stack change bit" and bits 1-15 contain the address of a 64-word vector table. Vector table entries are one word in length and consist of a "direct" bit in bit 0 followed by an address in bits 1-15.

An INTERRUPT ACKNOWLEDGE instruction is performed. The device code returned is added to the address of the vector table and the vector table entry at that address is fetched. If the direct bit in the fetched vector table entry is 0, the address in bits 1-15 is taken to be the address of the device handler routine for the interrupting device and control is immediately transferred there by placing the address in the program counter.

If the direct bit is 1, the address in bits 1-15 of the vector table entry is taken to be the address of the device control table (DCT) for the interrupting

device. At this point, the stack change bit is examined. If the stack change bit is 0, no stack change is performed. If the stack change bit is 1, a new stack is created by placing the contents of memory location 6 in the stack limit, and the contents of memory location 7 in the stack fault. The previous contents of memory locations  $40_8-43_8$ are then pushed onto this new stack.

Device control tables must consist of at least two words. The first word of a DCT consists of a "push bit" in bit 0 followed by the address of the device handler routine for the interrupting device in bits 1-15. The second word of a DCT contains a mask that will be used to construct the new interrupt priority mask. Succeeding words in a DCT may contain information that is to be used by the device interrupt handler.

After the stack change procedure is performed, the first word of the DCT is fetched and inspected. If the push bit is 1, a standard return block is pushed onto the stack with bits 1-15 of physical location 0 placed in bits 1-15 of the last word pushed. If the push bit is 0, no return block is pushed.

Following this procedure, the address of the DCT is placed in bits 1-15 of AC2 and bit 0 of AC2 is set to 0.

Next, the current interrupt priority mask is pushed on the stack. The contents of the second word of DCT are logically OR'd with the current interrupt priority mask and the result is placed in both AC0 and memory location 5. This constructs the new interrupt priority mask and places it in AC0 and the save location for the mask. A DOBS 0,CPU instruction is now performed. This is a MASK OUT instruction that also enables the interrupt system.

After a new interrupt priority mask is established and the interrupt system enabled, control is transferred to the device handler by placing bits 1-15 of the first word of the DCT in the program counter.

#### Use of the Vector Instruction

The VECTOR ON INTERRUPTING DEVICE CODE instruction is an extremely powerful instruction. Because of the impact of interrupt latency on overall system performance, and the impact of the VECTOR instruction on interrupt latency, this instruction should be well understood before it is used.

The VECTOR instruction can operate in any one of five modes. These modes are called mode A, mode B, mode C, mode D, and mode E. In general, as one goes through the modes, from A to E, the instruction performs more work, giving the user more power, but also takes more time to execute.